back to overview ▲

» DVM Test Report: Ac Analysis|Bode Plot|Vin Minimum|Light Load

| Test Details | |

| Schematic | LTC3406B- DVM ADVANCED.sxsch |

| Test | Ac Analysis|Bode Plot|Vin Minimum|Light Load |

| Date / Time | 2/7/2015 10:17:27 AM |

| Report Directory | dc_dc_built_in\AcAnalysis\Bode Plot\Vin Minimum\Light Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | FAIL |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 91.5107% |

| Power(LOAD1) | 45.1926m |

| Power(SRC1) | 49.3851m |

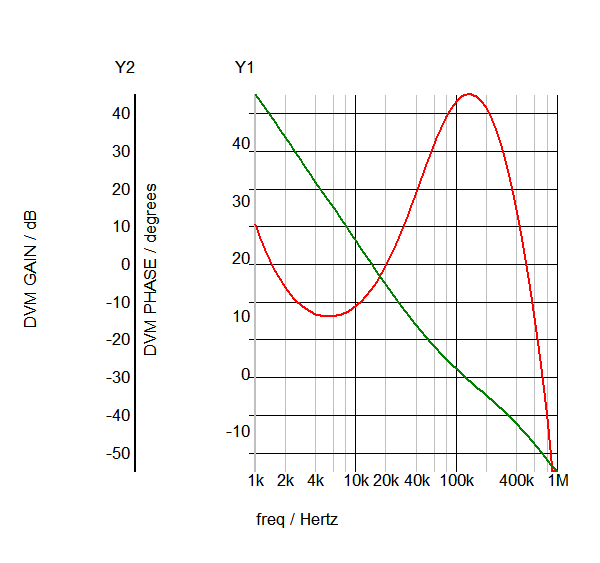

| gain_crossover_freq | 14.1768k |

| gain_margin | 50.1884 |

| min_phase | 9.90235 |

| phase_crossover_freq | 701.383k |

| min_phase_freq | 5.62341k |

| phase_margin | 14.6717 |

| sw_freq | 955.703k |

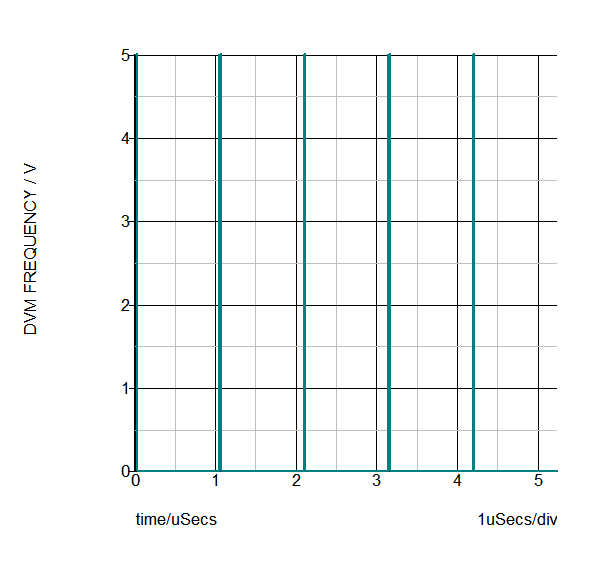

| FREQUENCY | AVG 100.286m MIN 0 MAX 5 RMS 708.117m |

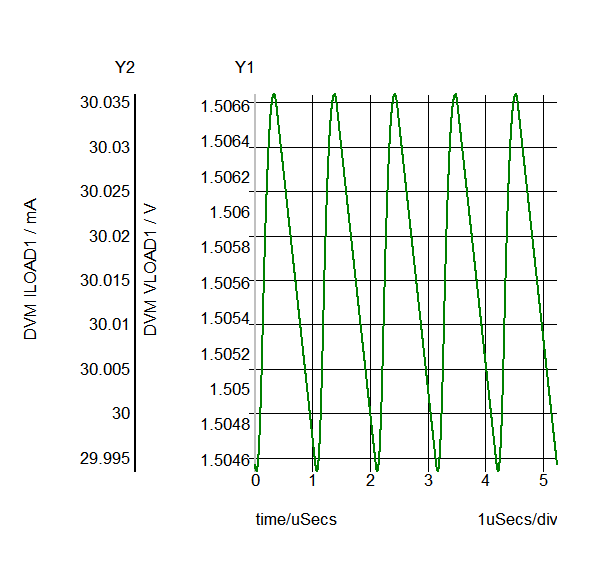

| ILOAD1 | AVG 30.0155m MIN 29.9934m MAX 30.0359m RMS 30.0155m |

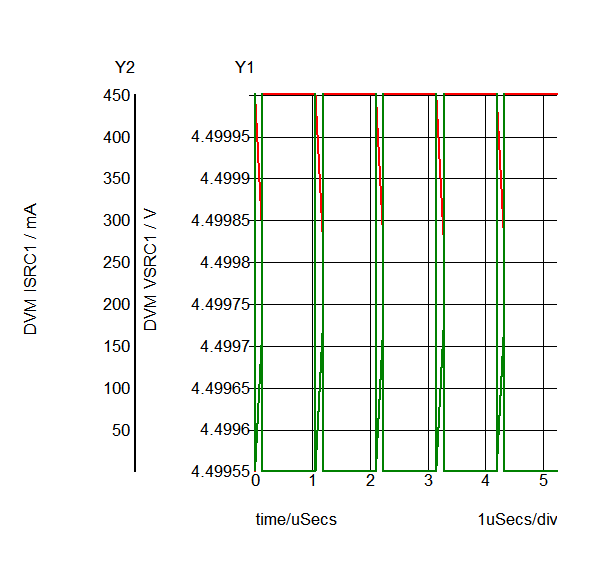

| ISRC1 | AVG 10.9747m MIN 277.708u MAX 450.136m RMS 35.0658m |

| VLOAD1 | AVG 1.50564 MIN 1.50453 MAX 1.50666 RMS 1.50564 |

| VSRC1 | AVG 4.49999 MIN 4.49955 MAX 4.5 RMS 4.49999 |

| Measured Spec Values | |

| Max_VLOAD1 | PASS: Max. Output1 Voltage (1.50666) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD1 | PASS: Min. Output1 Voltage (1.50453) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (50.1884) is greater than Min. Gain Margin (12) |

| min_phase_margin | FAIL: Phase Margin (14.6717) is not greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac4_181.sxgph |

LOAD1

VLOAD1

ILOAD1

|

|

| SXGPH File | simplis_pop4_167.sxgph |

SRC1

VSRC1

ISRC1

|

|

| SXGPH File | simplis_pop4_162.sxgph |

default

FREQUENCY

|

|

| SXGPH File | simplis_pop4_145.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop4_150.sxgph |

| DVM Bode Plot Input#log#ac | simplis_ac4_188.sxgph |