back to overview ▲

» DVM Test Report: Efficiency and Loop Characterization|Vin Maximum|100% Load

| Test Details | |

| Schematic | 8.2_LLCClosed Loop.sxsch |

| Test | Efficiency and Loop Characterization|Vin Maximum|100% Load |

| Date / Time | 2/7/2015 10:40:42 AM |

| Report Directory | measure_loop_param\Efficiencyand Loop Characterization\Vin Maximum\100% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 95.2439% |

| Frequency(CLK) | 92.718755kHertz |

| Power(LOAD) | 120.92 |

| Power(SRC) | 126.958 |

| eta_max | 95.2439% |

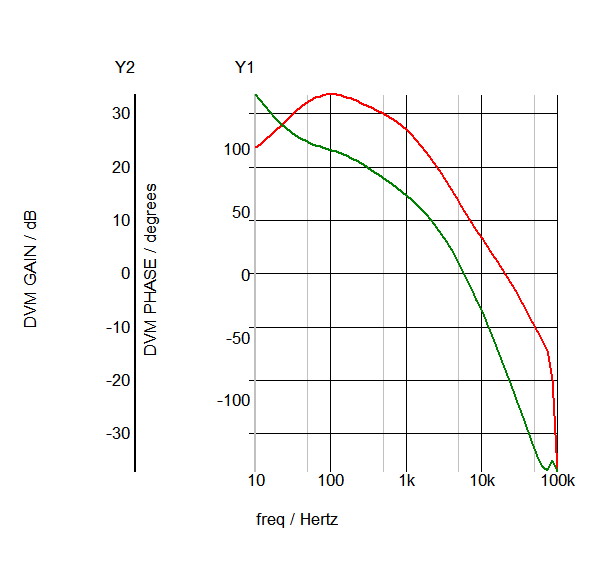

| gain_crossover_freq | 5.88124k |

| gain_margin | 18.429 |

| gmargin_max | 18.429 |

| gxover_max | 5.88124k |

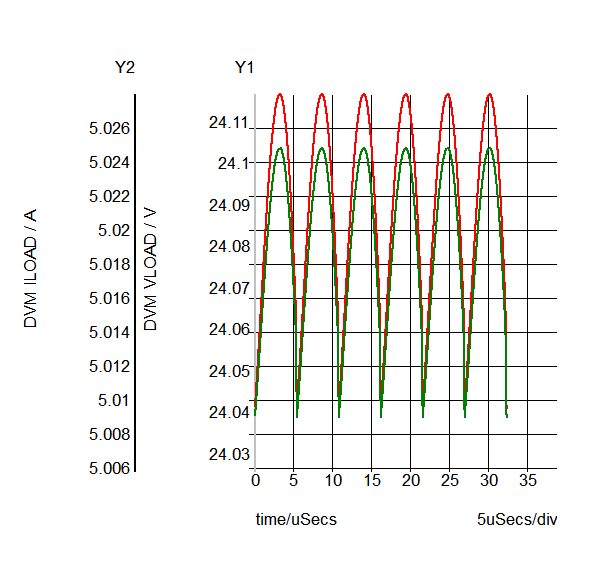

| iload_max | 5.01938 |

| min_phase | 50.9788 |

| phase_crossover_freq | 20.5968k |

| min_phase_freq | 5.88124k |

| phase_margin | 50.5732 |

| pmargin_max | 50.5732 |

| sw_freq_max | 92.718755kHertz |

| ICout | AVG 4.78499u MIN -5.00899 MAX 2.58954 RMS 2.24713 |

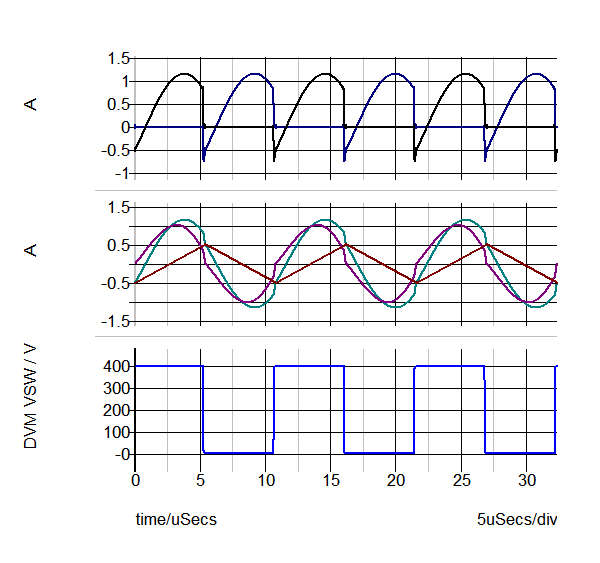

| IDQ1 | AVG 317.483m MIN -755.771m MAX 1.15709 RMS 588.071m |

| IDQ2 | AVG 317.443m MIN -755.475m MAX 1.1571 RMS 588.032m |

| ILOAD | AVG 5.01938 MIN 5.00899 MAX 5.0248 RMS 5.01938 |

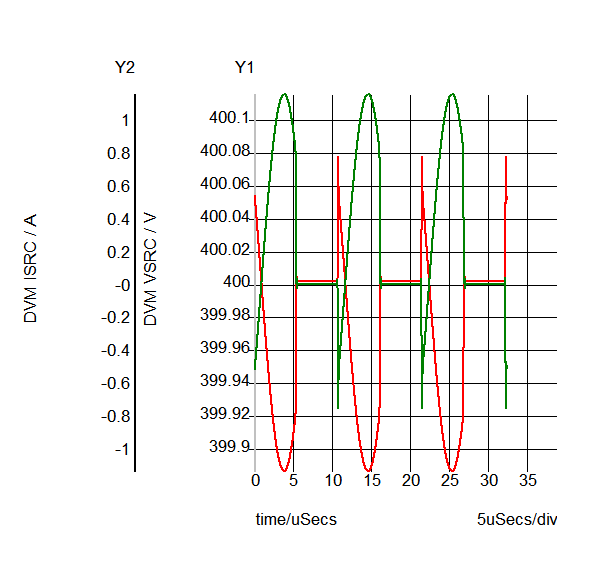

| ISRC | AVG 317.483m MIN -755.771m MAX 1.15709 RMS 588.071m |

| Im | AVG -93.3257u MIN -506.164m MAX 505.976m RMS 292.69m |

| Ip | AVG 133.319u MIN -1.0149 MAX 1.01525 RMS 733.515m |

| Ir | AVG 39.9936u MIN -1.1571 MAX 1.15709 RMS 832.684m |

| Is1 | AVG 2.51019 MIN -5.08994u MAX 7.61435 RMS 3.89078 |

| Is2 | AVG 2.50919 MIN -5.08995u MAX 7.61174 RMS 3.88932 |

| VLOAD | AVG 24.0906 MIN 24.0409 MAX 24.1166 RMS 24.0907 |

| VSRC | AVG 399.968 MIN 399.884 MAX 400.076 RMS 399.968 |

| VSW | AVG 199.968 MIN -736.051m MAX 400.81 RMS 282.183 |

| Vs | AVG -100.388m MIN -25.2408 MAX 24.9363 RMS 24.9756 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (24.1166) is less than or equal to Max. Output1 Voltage Spec (25.2) |

| Min_VLOAD | PASS: Min. Output1 Voltage (24.0409) is greater than or equal to Min. Output1 Voltage Spec (22.8) |

| min_gain_margin | PASS: Gain Margin (18.429) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (50.5732) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac28_1809.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop28_1775.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop28_1765.sxgph |

Primary

IDQ1

IDQ2

Im

Ip

Ir

VSW

|

|

| SXGPH File | simplis_pop28_1756.sxgph |

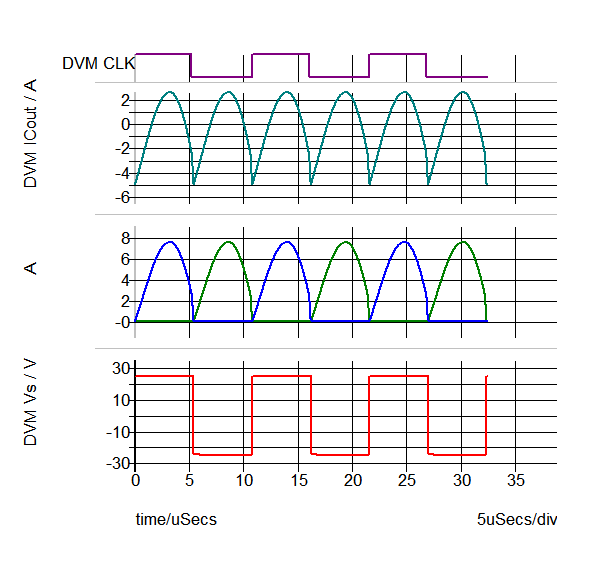

Secondary

CLK

ICout

Is1

Is2

Vs

|

|

| SXGPH File | simplis_pop28_1770.sxgph |

| Other SXGPH Files | |

| default#1798#pop | simplis_pop28_1798.sxgph |

| Modulator#pop | simplis_pop28_1803.sxgph |

| DVM Bode Plot Input#log#ac | simplis_ac28_1816.sxgph |