back to overview ▲

» DVM Test Report: Efficiency and Loop Characterization|Vin Maximum|5% Load

| Test Details | |

| Schematic | 8.2_LLCClosed Loop.sxsch |

| Test | Efficiency and Loop Characterization|Vin Maximum|5% Load |

| Date / Time | 2/7/2015 10:37:51 AM |

| Report Directory | measure_loop_param\Efficiencyand Loop Characterization\Vin Maximum\5% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 94.5907% |

| Frequency(CLK) | 102.53661kHertz |

| Power(LOAD) | 6.06146 |

| Power(SRC) | 6.4081 |

| eta_max | 94.5907% |

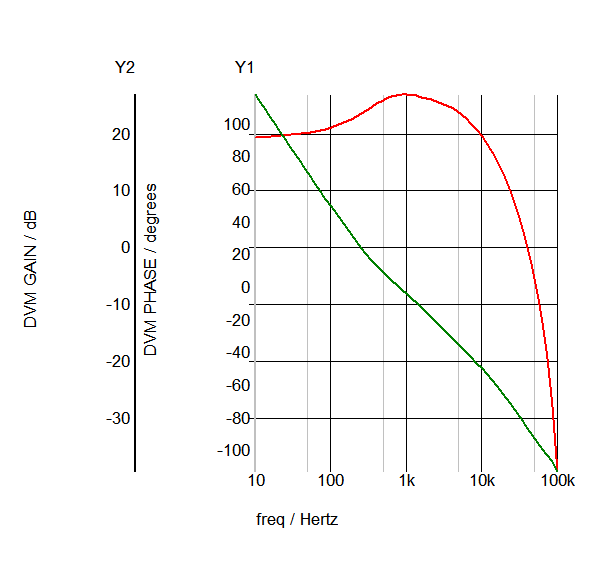

| gain_crossover_freq | 247.419 |

| gain_margin | 33.9831 |

| gmargin_max | 33.9831 |

| gxover_max | 247.419 |

| iload_max | 251.543m |

| min_phase | 96.9774 |

| phase_crossover_freq | 52.0421k |

| min_phase_freq | 91.3835 |

| phase_margin | 106.052 |

| pmargin_max | 106.052 |

| sw_freq_max | 102.53661kHertz |

| ICout | AVG 4.81771u MIN -251.521m MAX 331.902m RMS 223.444m |

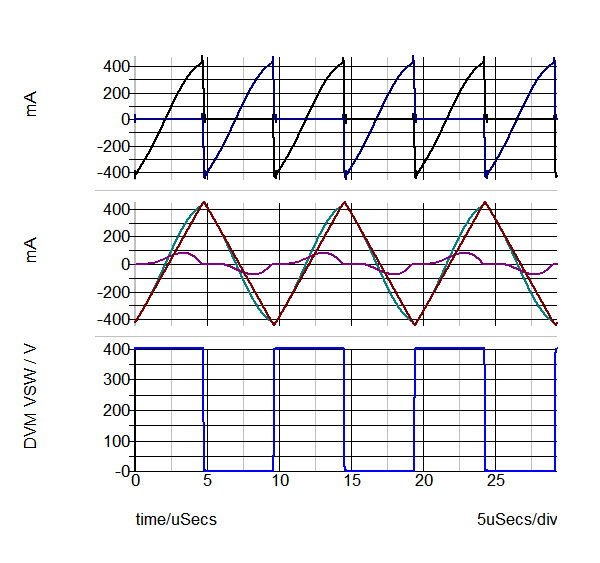

| IDQ1 | AVG 16.0301m MIN -452.019m MAX 473.724m RMS 198.063m |

| IDQ2 | AVG 15.9901m MIN -456.322m MAX 472.667m RMS 198.067m |

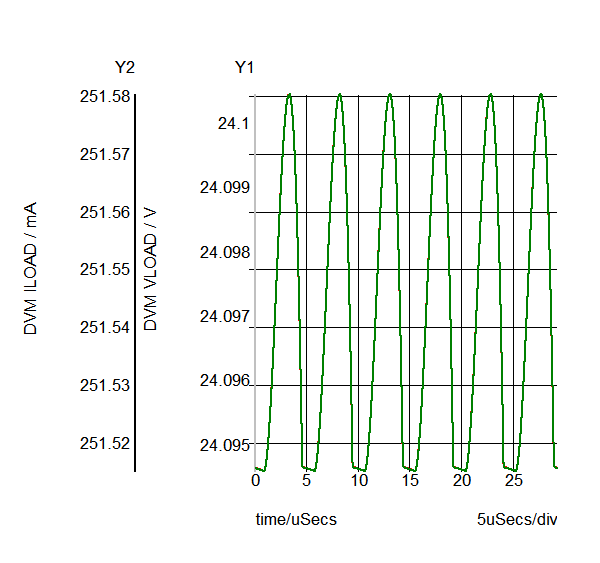

| ILOAD | AVG 251.543m MIN 251.515m MAX 251.58m RMS 251.543m |

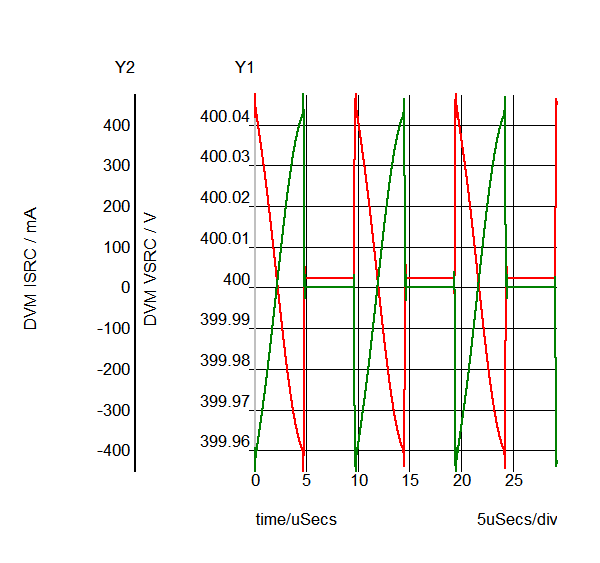

| ISRC | AVG 16.0301m MIN -452.019m MAX 473.724m RMS 198.063m |

| Im | AVG 25.5221u MIN -445.403m MAX 445.425m RMS 261.178m |

| Ip | AVG 14.4775u MIN -77.752m MAX 77.799m RMS 44.8642m |

| Ir | AVG 39.9996u MIN -445.403m MAX 445.425m RMS 282.027m |

| Is1 | AVG 125.828m MIN -5.04374u MAX 583.487m RMS 238.013m |

| Is2 | AVG 125.72m MIN -5.04375u MAX 583.135m RMS 237.838m |

| VLOAD | AVG 24.0971 MIN 24.0946 MAX 24.1004 RMS 24.0971 |

| VSRC | AVG 399.998 MIN 399.953 MAX 400.045 RMS 399.998 |

| VSW | AVG 199.998 MIN -718.147m MAX 400.761 RMS 282.295 |

| Vs | AVG -5.02765m MIN -24.8089 MAX 24.7856 RMS 24.3677 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (24.1004) is less than or equal to Max. Output1 Voltage Spec (25.2) |

| Min_VLOAD | PASS: Min. Output1 Voltage (24.0946) is greater than or equal to Min. Output1 Voltage Spec (22.8) |

| min_gain_margin | PASS: Gain Margin (33.9831) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (106.052) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac15_964.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop15_941.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop15_931.sxgph |

Primary

IDQ1

IDQ2

Im

Ip

Ir

VSW

|

|

| SXGPH File | simplis_pop15_911.sxgph |

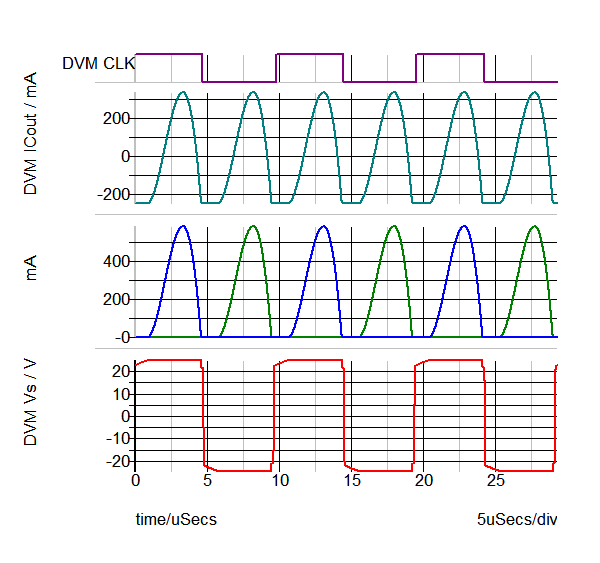

Secondary

CLK

ICout

Is1

Is2

Vs

|

|

| SXGPH File | simplis_pop15_936.sxgph |

| Other SXGPH Files | |

| default#919#pop | simplis_pop15_919.sxgph |

| Modulator#pop | simplis_pop15_924.sxgph |

| DVM Bode Plot Input#log#ac | simplis_ac15_971.sxgph |