back to overview ▲

» DVM Test Report: Efficiency and Loop Characterization|Vin Minimum|35% Load

| Test Details | |

| Schematic | 8.2_LLCClosed Loop.sxsch |

| Test | Efficiency and Loop Characterization|Vin Minimum|35% Load |

| Date / Time | 2/7/2015 10:42:14 AM |

| Report Directory | measure_loop_param\Efficiencyand Loop Characterization\Vin Minimum\35% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 95.8073% |

| Frequency(CLK) | 79.716352kHertz |

| Power(LOAD) | 42.3473 |

| Power(SRC) | 44.2005 |

| eta_min | 95.8073% |

| gain_crossover_freq | 4.83002k |

| gain_margin | 25.9067 |

| gmargin_min | 25.9067 |

| gxover_min | 4.83002k |

| iload_min | 1.75744 |

| min_phase | 45.6699 |

| phase_crossover_freq | 30.3318k |

| min_phase_freq | 4.83002k |

| phase_margin | 45.4158 |

| pmargin_min | 45.4158 |

| sw_freq_min | 79.716352kHertz |

| ICout | AVG 4.81361u MIN -1.75617 MAX 1.48536 RMS 1.14143 |

| IDQ1 | AVG 122.81m MIN -568.007m MAX 659.923m RMS 335.671m |

| IDQ2 | AVG 122.774m MIN -567.716m MAX 659.982m RMS 335.656m |

| ILOAD | AVG 1.75744 MIN 1.75616 MAX 1.75854 RMS 1.75744 |

| ISRC | AVG 122.81m MIN -568.007m MAX 659.923m RMS 335.671m |

| Im | AVG -132.087u MIN -572.533m MAX 572.262m RMS 337.72m |

| Ip | AVG 168.085u MIN -432.057m MAX 432.521m RMS 279.474m |

| Ir | AVG 35.9976u MIN -659.979m MAX 659.92m RMS 475.744m |

| Is1 | AVG 879.353m MIN -5.06462u MAX 3.2439 RMS 1.48307 |

| Is2 | AVG 878.093m MIN -5.06465u MAX 3.24042 RMS 1.48119 |

| VLOAD | AVG 24.096 MIN 24.0785 MAX 24.1109 RMS 24.096 |

| VSRC | AVG 359.988 MIN 359.934 MAX 360.057 RMS 359.988 |

| VSW | AVG 179.988 MIN -727.391m MAX 360.783 RMS 254.137 |

| Vs | AVG -35.1737m MIN -25.0009 MAX 24.8715 RMS 24.4146 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (24.1109) is less than or equal to Max. Output1 Voltage Spec (25.2) |

| Min_VLOAD | PASS: Min. Output1 Voltage (24.0785) is greater than or equal to Min. Output1 Voltage Spec (22.8) |

| min_gain_margin | PASS: Gain Margin (25.9067) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (45.4158) is greater than Min. Phase Margin (35) |

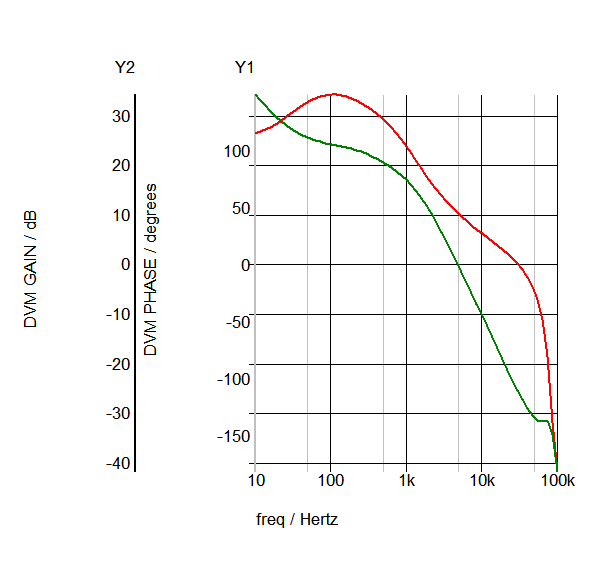

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac35_2264.sxgph |

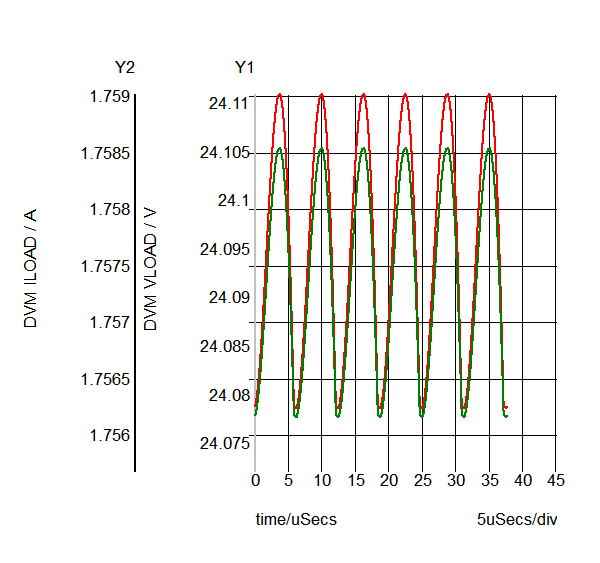

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop35_2230.sxgph |

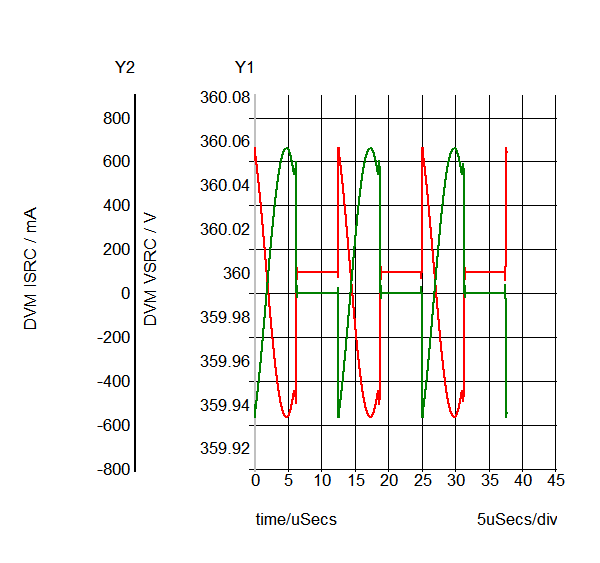

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop35_2220.sxgph |

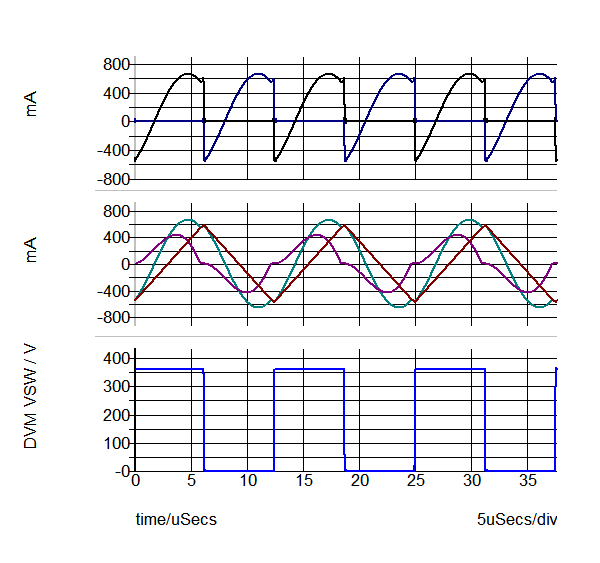

Primary

IDQ1

IDQ2

Im

Ip

Ir

VSW

|

|

| SXGPH File | simplis_pop35_2211.sxgph |

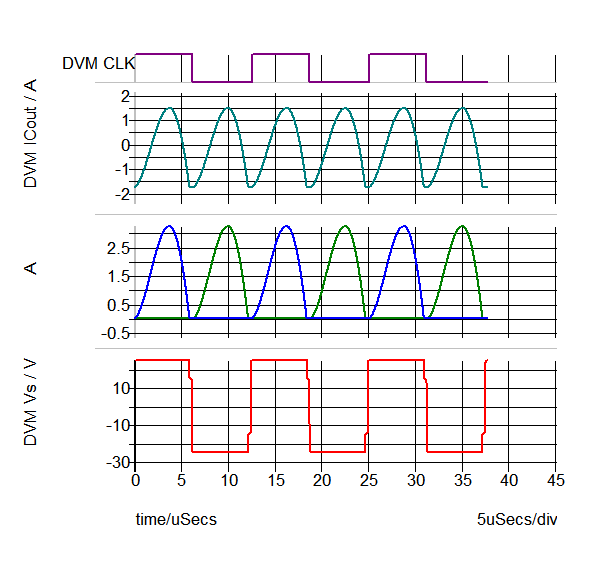

Secondary

CLK

ICout

Is1

Is2

Vs

|

|

| SXGPH File | simplis_pop35_2225.sxgph |

| Other SXGPH Files | |

| default#2253#pop | simplis_pop35_2253.sxgph |

| Modulator#pop | simplis_pop35_2258.sxgph |

| DVM Bode Plot Input#log#ac | simplis_ac35_2271.sxgph |