back to overview ▲

» DVM Test Report: Efficiency and Loop Characterization|Vin Nominal|40% Load

| Test Details | |

| Schematic | 8.2_LLCClosed Loop.sxsch |

| Test | Efficiency and Loop Characterization|Vin Nominal|40% Load |

| Date / Time | 2/7/2015 10:36:20 AM |

| Report Directory | measure_loop_param\Efficiencyand Loop Characterization\Vin Nominal\40% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 95.8977% |

| Frequency(CLK) | 87.150975kHertz |

| Power(LOAD) | 48.3997 |

| Power(SRC) | 50.4702 |

| eta_nom | 95.8977% |

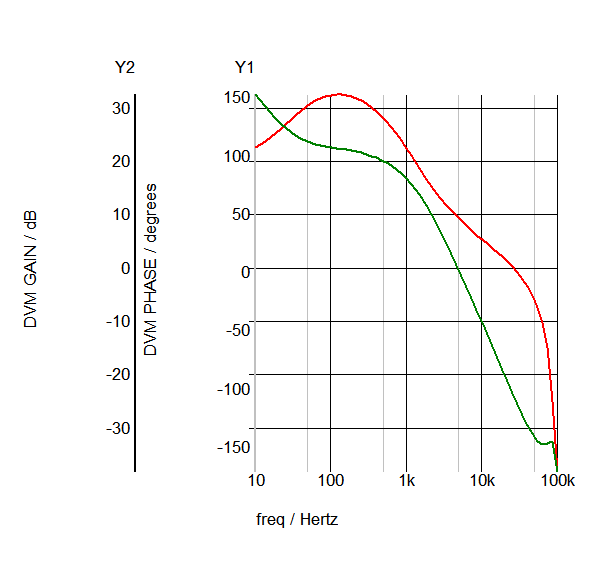

| gain_crossover_freq | 4.81162k |

| gain_margin | 25.4461 |

| gmargin_nom | 25.4461 |

| gxover_nom | 4.81162k |

| iload_nom | 2.00855 |

| min_phase | 47.1751 |

| phase_crossover_freq | 28.8776k |

| min_phase_freq | 4.81162k |

| phase_margin | 46.9325 |

| pmargin_nom | 46.9325 |

| sw_freq_nom | 87.150975kHertz |

| ICout | AVG 4.79923u MIN -2.00688 MAX 1.37908 RMS 1.10673 |

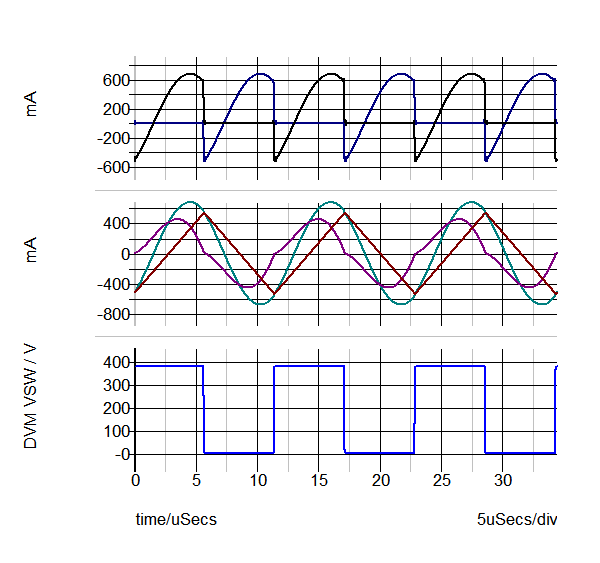

| IDQ1 | AVG 132.846m MIN -533.964m MAX 676.374m RMS 338.215m |

| IDQ2 | AVG 132.808m MIN -533.855m MAX 676.439m RMS 338.194m |

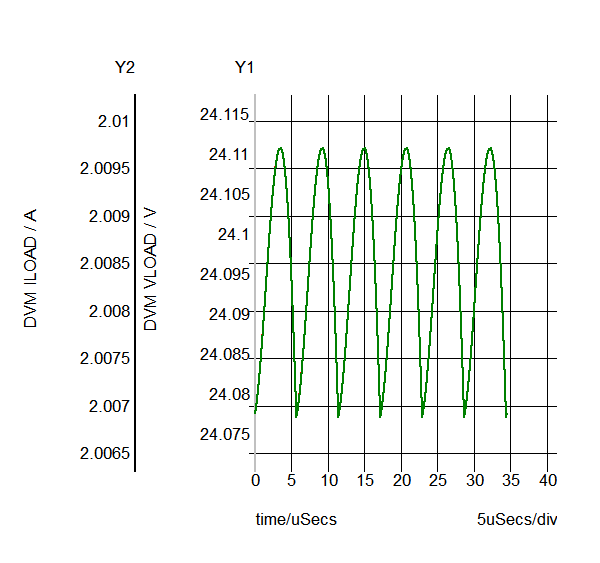

| ILOAD | AVG 2.00855 MIN 2.00688 MAX 2.00971 RMS 2.00855 |

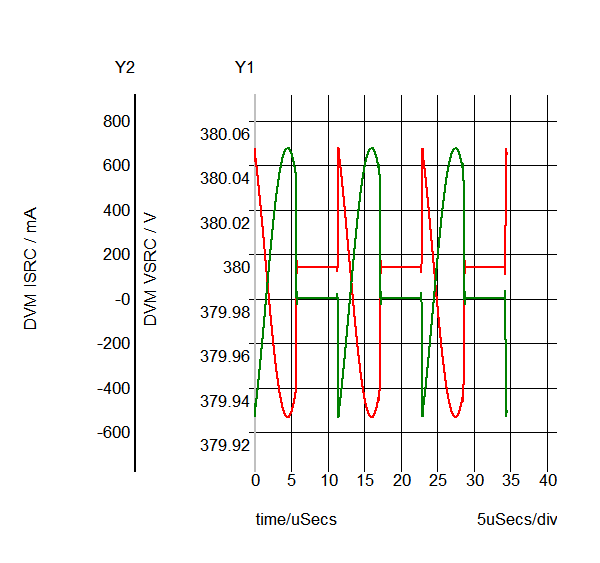

| ISRC | AVG 132.846m MIN -533.964m MAX 676.374m RMS 338.215m |

| Im | AVG -106.791u MIN -535.889m MAX 535.673m RMS 309.751m |

| Ip | AVG 144.788u MIN -451.459m MAX 451.84m RMS 305.832m |

| Ir | AVG 37.9974u MIN -676.435m MAX 676.37m RMS 479.422m |

| Is1 | AVG 1.00482 MIN -5.06561u MAX 3.3888 RMS 1.62271 |

| Is2 | AVG 1.00373 MIN -5.06564u MAX 3.38594 RMS 1.62112 |

| VLOAD | AVG 24.0969 MIN 24.077 MAX 24.1107 RMS 24.0969 |

| VSRC | AVG 379.987 MIN 379.932 MAX 380.053 RMS 379.987 |

| VSW | AVG 189.987 MIN -724.524m MAX 380.777 RMS 268.2 |

| Vs | AVG -40.339m MIN -25.0107 MAX 24.8754 RMS 24.8548 |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (24.1107) is less than or equal to Max. Output1 Voltage Spec (25.2) |

| Min_VLOAD | PASS: Min. Output1 Voltage (24.077) is greater than or equal to Min. Output1 Voltage Spec (22.8) |

| min_gain_margin | PASS: Gain Margin (25.4461) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (46.9325) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac8_509.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop8_475.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop8_465.sxgph |

Primary

IDQ1

IDQ2

Im

Ip

Ir

VSW

|

|

| SXGPH File | simplis_pop8_456.sxgph |

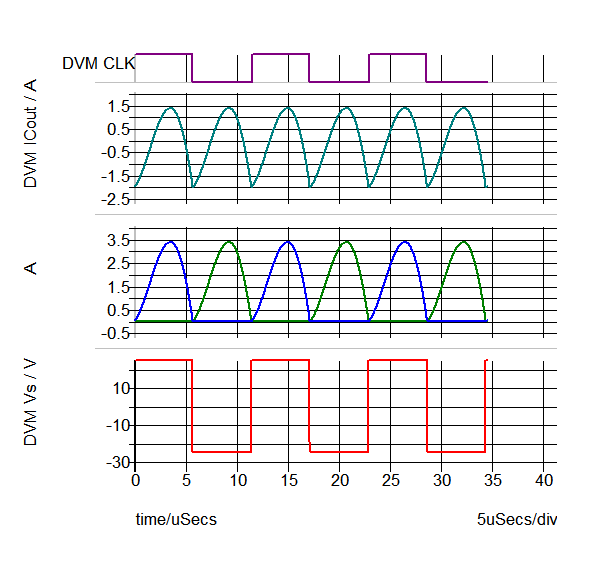

Secondary

CLK

ICout

Is1

Is2

Vs

|

|

| SXGPH File | simplis_pop8_470.sxgph |

| Other SXGPH Files | |

| DVM Bode Plot Input#log#ac | simplis_ac8_516.sxgph |

| default#498#pop | simplis_pop8_498.sxgph |

| Modulator#pop | simplis_pop8_503.sxgph |