SIMPLIS Parts

|

The Sampler and Zero Order Hold models an analog sample and hold. On each clock edge, the input voltage is sampled and held until the next clock edge. As with the other devices in the Discrete Time Filter category, the Sampler and Zero Order Hold is compatible with the SIMPLIS POP and AC Analyses.

Related topics:

In this Topic Hide

Model Name: |

Sampler and Zero order Hold |

|

Simulator: |

|

This device is compatible with the SIMPLIS simulator. |

Parts Selector |

Digital Functions | Discrete Time Filters |

|

Symbol Library: |

None - the symbol is automatically generated when placed or edited. |

|

Model File: |

None - the device model is generated before simulation. |

|

Subcircuit Name: |

SIMPLIS_DIGI1_D_DF_SNH_Y |

|

Symbols: |

|

|

Multiple Selections: |

Only one device at a time can be edited. |

|

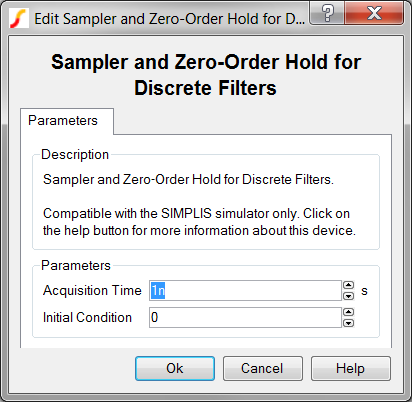

To configure the sampler and zero order hold, follow these steps:

| Label | Parameter Description |

Acquisition Time |

Filter acquisition time in seconds |

Initial Condition |

Initial condition of the filter output |

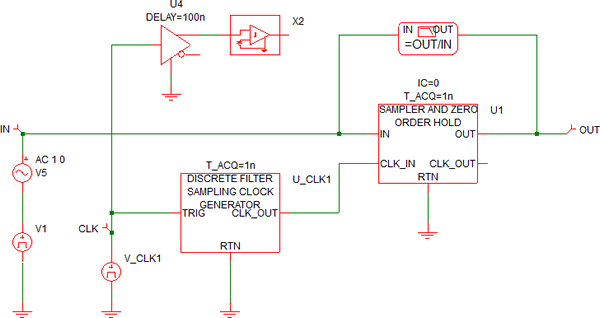

The test circuit used to generate the waveform examples in the next section can be downloaded here: simplis_036_samplehold_example.sxsch.

In the circuit example, a 100kHz sine wave with a 1V amplitude ( +/- 1V peak ) is applied to the input of the sampler and hold. The clock has a frequency of 1MHz, and the sampled input voltage is output on the same graph as the input voltage.

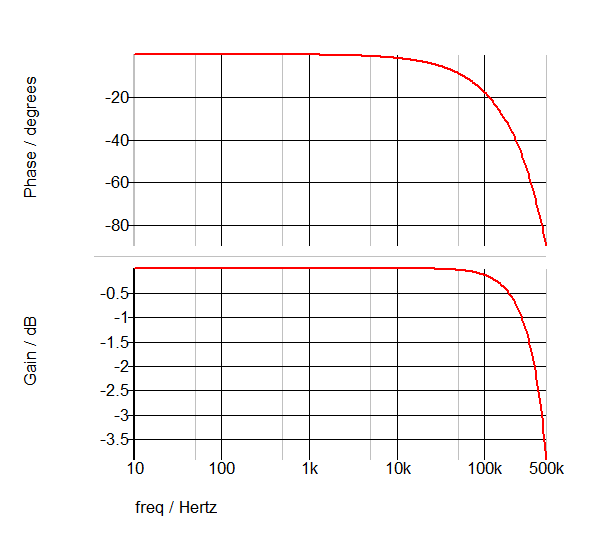

The following AC waveforms confirm that the DC gain is 0dB and the phase change at 1/2 the sampling frequency is the expected 90 degrees.

Because this sampler and zero order hold model is generated by a template script when the simulation is executed, a fixed model cannot be inserted into a netlist. The template script for this device is simplis_make_digital_filter_model.sxscr, which you, as a licensed user, can download in a zip archive of all built-in scripts.

To download this zip file, follow these steps:

Note: You will be prompted to log in with the user name and password given to you when you registered.