back to overview ▲

» DVM Test Report: VOUT=0.6V|Bode Plot|Vin Maximum|50% Load

| Test Details | |

| Schematic | 6.3_LTC3406B - DVM ADVANCED.sxsch |

| Test | VOUT=0.6V|Bode Plot|Vin Maximum|50% Load |

| Date / Time | 12/10/2015 5:51 PM |

| Report Directory | promote_scalars\VOUT=0.6V\BodePlot\Vin Maximum\50% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | FAIL |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 76.7746% |

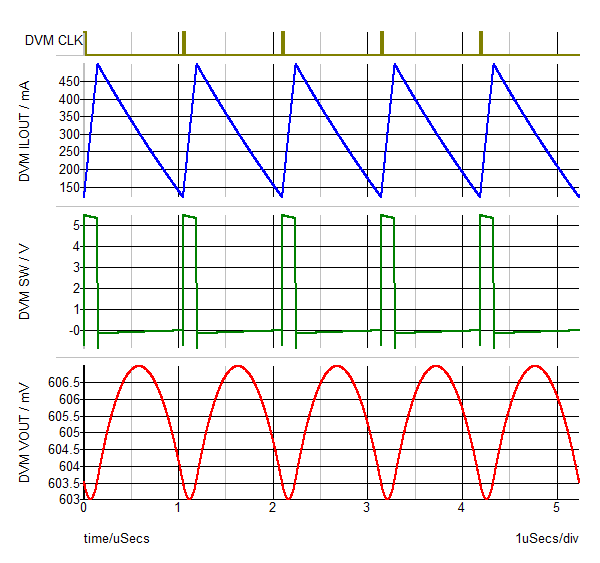

| Frequency(CLK) | 955.697k |

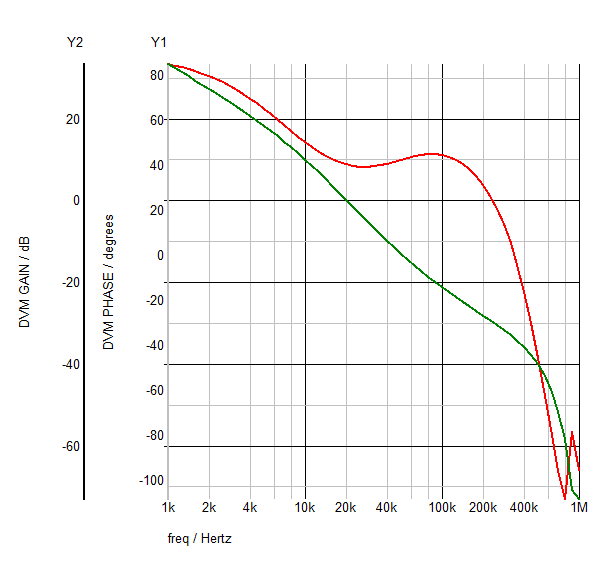

| gain_crossover_freq | 19.9547k |

| gain_margin | 33.8124 |

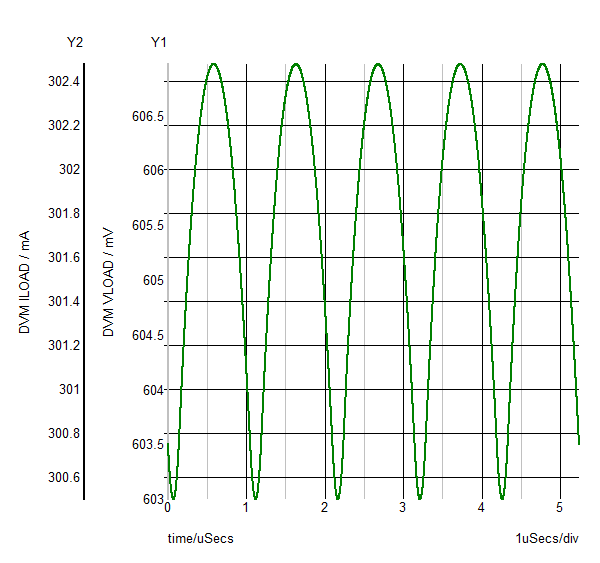

| ILOAD | AVG 301.724m MIN 300.497m MAX 302.474m RMS 301.724m PK2PK 1.97741m |

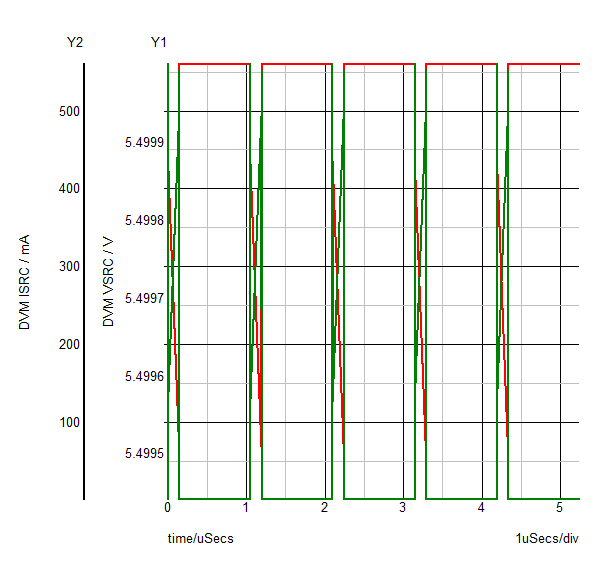

| ISRC | AVG 43.2657m MIN 465.564u MAX 559.124m RMS 122.249m PK2PK 558.659m |

| min_phase | 39.869 |

| min_phase_freq | 19.9547k |

| phase_crossover_freq | 335.599k |

| phase_margin | 39.8687 |

| Power(LOAD) | 182.683m |

| Power(SRC) | 237.946m |

| VLOAD | AVG 605.46m MIN 602.998m MAX 606.966m RMS 605.461m PK2PK 3.96798m |

| VSRC | AVG 5.49996 MIN 5.49944 MAX 5.5 RMS 5.49996 PK2PK 558.659u |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (606.966m) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | FAIL: Min. Output1 Voltage (602.998m) is not greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (33.8124) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (39.8687) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac4_197.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop5_180.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop5_170.sxgph |

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop5_175.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop5_162.sxgph |