back to overview ▲

» DVM Test Report: Steady-State|Steady-State|Vin Maximum|50%

| Test Details | |

| Schematic | 4.2_LTC3406B - DVM ADVANCED.sxsch |

| Test | Steady-State|Steady-State|Vin Maximum|50% |

| Date / Time | 12/10/2015 5:45 PM |

| Report Directory | run_blt_in_and_prmt_grphs\Steady-State\Steady-State\VinMaximum\50% |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 79.0058% |

| Efficiency_Max | 79.0058% |

| Frequency(CLK) | 955.651k |

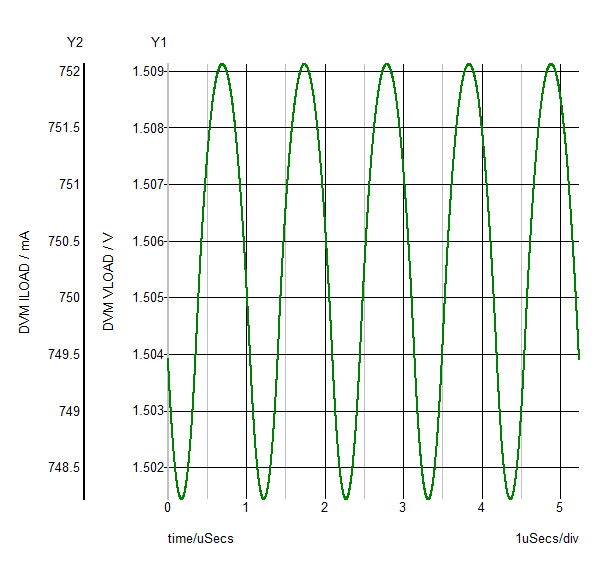

| ILOAD | AVG 750.338m MIN 748.216m MAX 752.056m RMS 750.339m PK2PK 3.83952m |

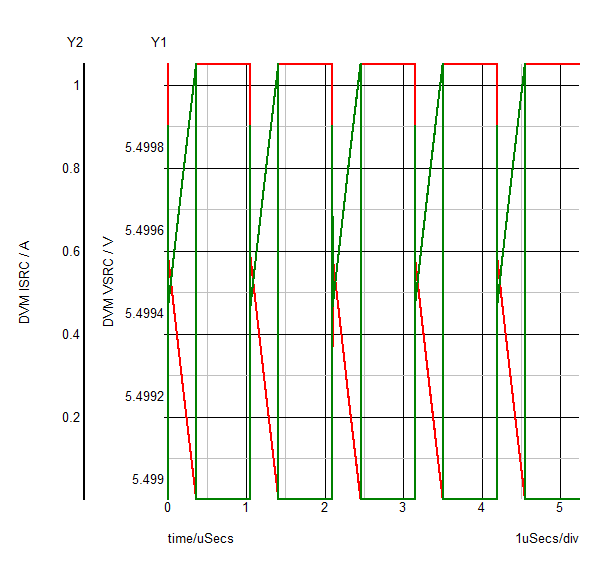

| ISRC | AVG 260.034m MIN 465.747u MAX 1.0488 RMS 454.793m PK2PK 1.04833 |

| Power(LOAD) | 1.12977 |

| Power(SRC) | 1.42998 |

| VLOAD | AVG 1.50567 MIN 1.50142 MAX 1.50912 RMS 1.50568 PK2PK 7.7046m |

| VSRC | AVG 5.49974 MIN 5.49895 MAX 5.5 RMS 5.49974 PK2PK 1.04833m |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (1.50912) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | PASS: Min. Output1 Voltage (1.50142) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop17_579.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop17_569.sxgph |

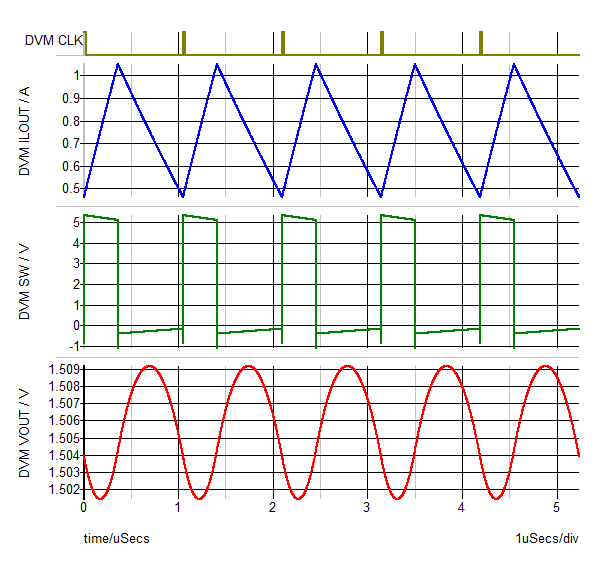

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop17_574.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop17_561.sxgph |