back to overview ▲

» DVM Test Report: VOUT=0.6V|Bode Plot|Vin Nominal|100% Load

| Test Details | |

| Schematic | 6.3_LTC3406B - DVM ADVANCED.sxsch |

| Test | VOUT=0.6V|Bode Plot|Vin Nominal|100% Load |

| Date / Time | 12/10/2015 5:55 PM |

| Report Directory | use_extract_curve\VOUT=0.6V\BodePlot\Vin Nominal\100% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | FAIL |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 65.4094% |

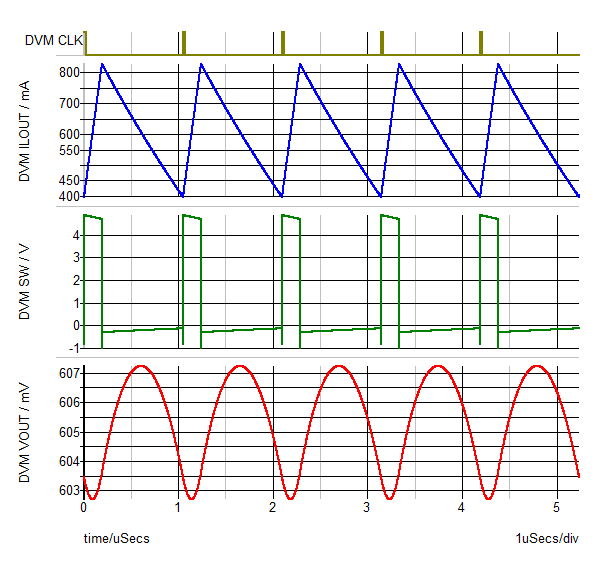

| Frequency(CLK) | 955.684k |

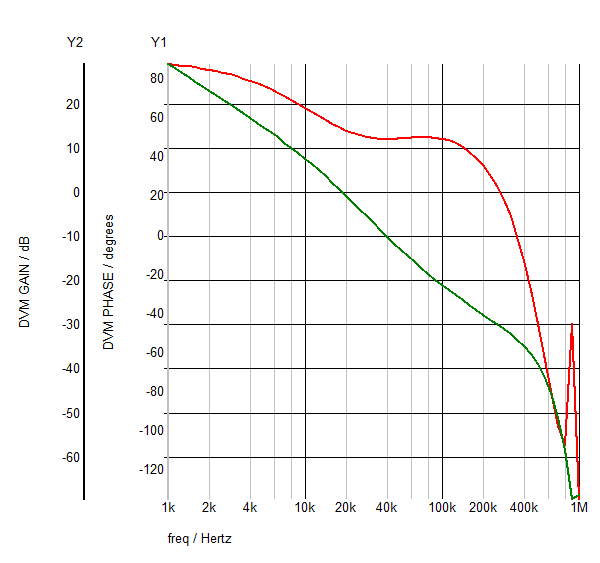

| gain_crossover_freq | 18.4307k |

| gain_margin | 33.542 |

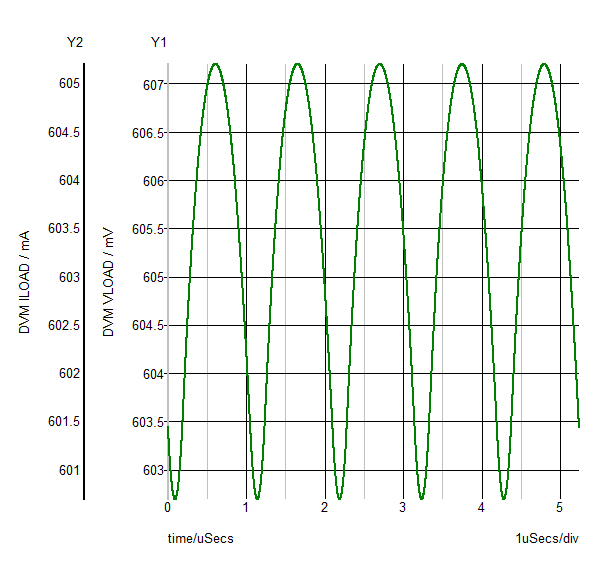

| ILOAD | AVG 603.42m MIN 600.692m MAX 605.194m RMS 603.422m PK2PK 4.50208m |

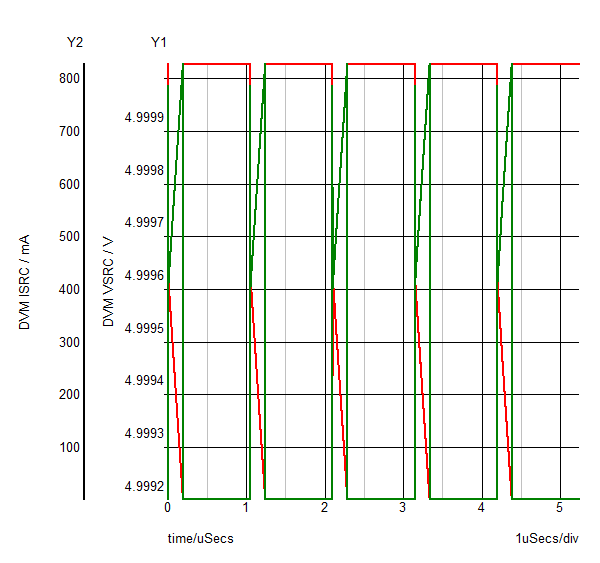

| ISRC | AVG 111.72m MIN 423.369u MAX 826.283m RMS 266.443m PK2PK 825.86m |

| min_phase | 54.1119 |

| min_phase_freq | 18.4307k |

| phase_crossover_freq | 350.117k |

| phase_margin | 54.0166 |

| Power(LOAD) | 365.33m |

| Power(SRC) | 558.529m |

| VLOAD | AVG 605.429m MIN 602.692m MAX 607.209m RMS 605.431m PK2PK 4.51706m |

| VSRC | AVG 4.99989 MIN 4.99917 MAX 5 RMS 4.99989 PK2PK 825.86u |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (607.209m) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | FAIL: Min. Output1 Voltage (602.692m) is not greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (33.542) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (54.0166) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac5_239.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop6_222.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop6_212.sxgph |

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop6_217.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop6_204.sxgph |