back to overview ▲

» DVM Test Report: Ac Analysis|Bode Plot|Vin Maximum|Light Load

| Test Details | |

| Schematic | LTC3406B - DVM ADVANCED.sxsch |

| Test | Ac Analysis|Bode Plot|Vin Maximum|Light Load |

| Date / Time | 12/10/2015 5:40 PM |

| Report Directory | dc_dc_built_in\AcAnalysis\Bode Plot\Vin Maximum\Light Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | FAIL |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

| Efficiency | 90.7824% |

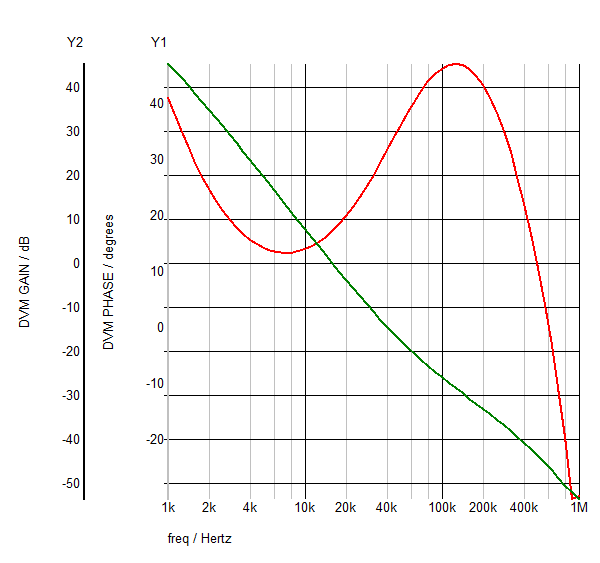

| gain_crossover_freq | 15.7147k |

| gain_margin | 46.4358 |

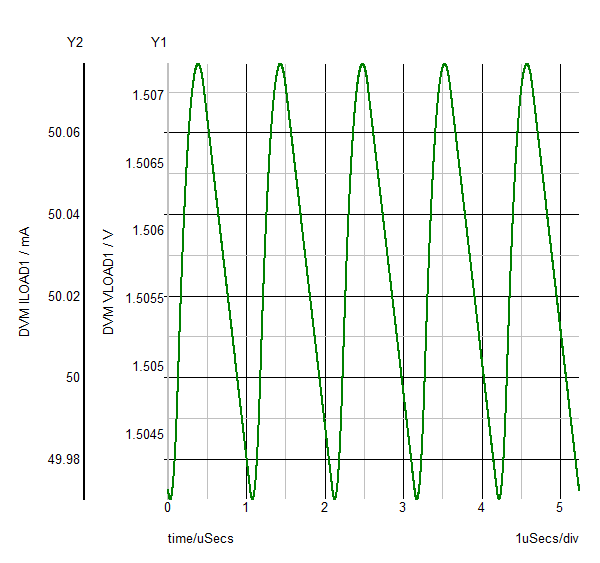

| ILOAD1 | AVG 50.0271m MIN 49.9701m MAX 50.0766m RMS 50.0271m PK2PK 106.57u |

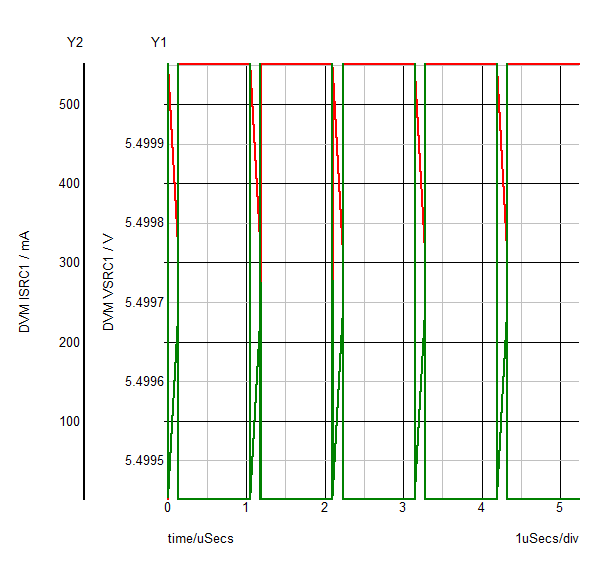

| ISRC1 | AVG 15.0869m MIN 349.963u MAX 550.21m RMS 47.9309m PK2PK 549.86m |

| min_phase | 13.1179 |

| min_phase_freq | 7.07946k |

| phase_crossover_freq | 599.426k |

| phase_margin | 16.9099 |

| Power(LOAD1) | 75.3274m |

| Power(SRC1) | 82.9758m |

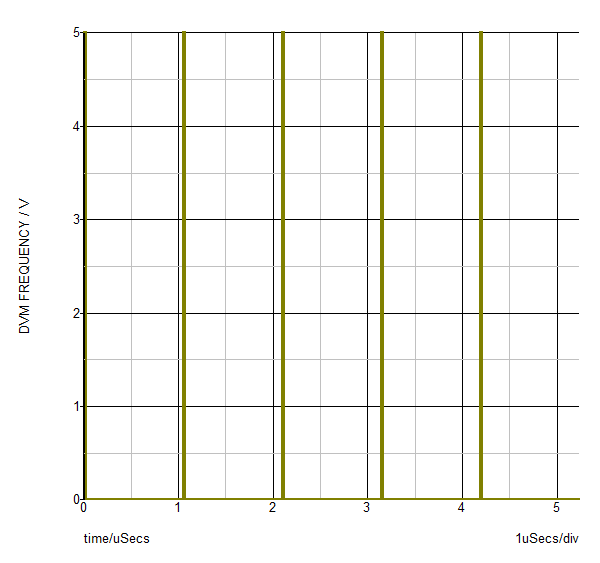

| sw_freq | 955.703k |

| VLOAD1 | AVG 1.50573 MIN 1.50402 MAX 1.50722 RMS 1.50573 PK2PK 3.20747m |

| VSRC1 | AVG 5.49998 MIN 5.49945 MAX 5.5 RMS 5.49998 PK2PK 549.86u |

| Measured Spec Values | |

| Max_VLOAD1 | PASS: Max. Output1 Voltage (1.50722) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD1 | PASS: Min. Output1 Voltage (1.50402) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (46.4358) is greater than Min. Gain Margin (12) |

| min_phase_margin | FAIL: Phase Margin (16.9099) is not greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac7_295.sxgph |

LOAD1

VLOAD1

ILOAD1

|

|

| SXGPH File | simplis_pop7_281.sxgph |

SRC1

VSRC1

ISRC1

|

|

| SXGPH File | simplis_pop7_276.sxgph |

default

FREQUENCY

|

|

| SXGPH File | simplis_pop7_259.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop7_264.sxgph |