back to overview ▲

» DVM Test Report: Ac Analysis|Bode Plot|Vin Maximum|100% Load

| Test Details | |

| Schematic | 6.6.2_LTC3406B - DVM ADVANCED.sxsch |

| Test | Ac Analysis|Bode Plot|Vin Maximum|100% Load |

| Date / Time | 12/10/2015 5:53 PM |

| Report Directory | use_arbitrary_bodeplot\AcAnalysis\Bode Plot\Vin Maximum\100% Load |

| Log File | report.txt |

| Screenshot | schematic.png |

| Status | PASS |

| Simulator | simplis |

| Deck | input.deck |

| Init | input.deck.init |

| Measured Scalar Values | |

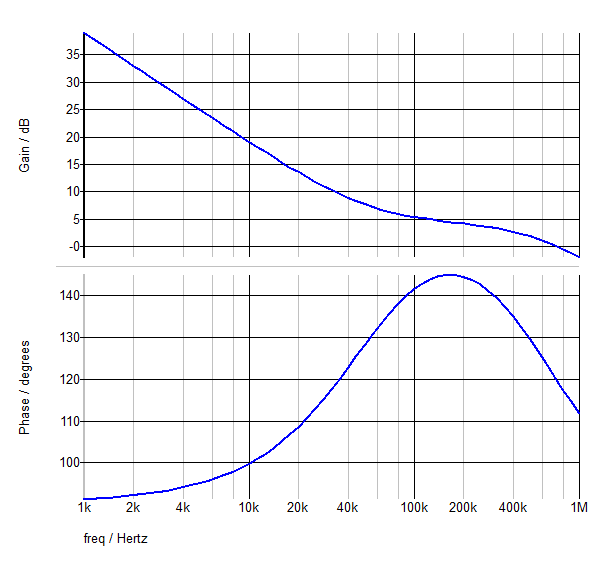

| DVM_Error_Amplifier_Gain_gain_crossover_freq | 718.233k |

| DVM_Error_Amplifier_Gain_high_pass_freq | -1 |

| DVM_Error_Amplifier_Gain_low_pass_freq | -1 |

| DVM_Error_Amplifier_Gain_max_gain | 38.8179 |

| DVM_Error_Amplifier_Gain_max_gain_freq | 1k |

| DVM_Error_Amplifier_Gain_min_gain | -2.0408 |

| DVM_Error_Amplifier_Gain_min_gain_freq | 1Meg |

| DVM_Error_Amplifier_Gain_passband | 0 |

| DVM_Error_Amplifier_Phase_max_phase | 144.731 |

| DVM_Error_Amplifier_Phase_max_phase_freq | 158.489k |

| DVM_Error_Amplifier_Phase_min_phase_before_crossover | 91.1119 |

| DVM_Error_Amplifier_Phase_min_phase_before_crossover_freq | 1k |

| DVM_Error_Amplifier_Phase_phase_margin | 120.19 |

| Efficiency | 66.3459% |

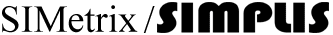

| gain_crossover_freq | 21.6616k |

| gain_margin | 26.8904 |

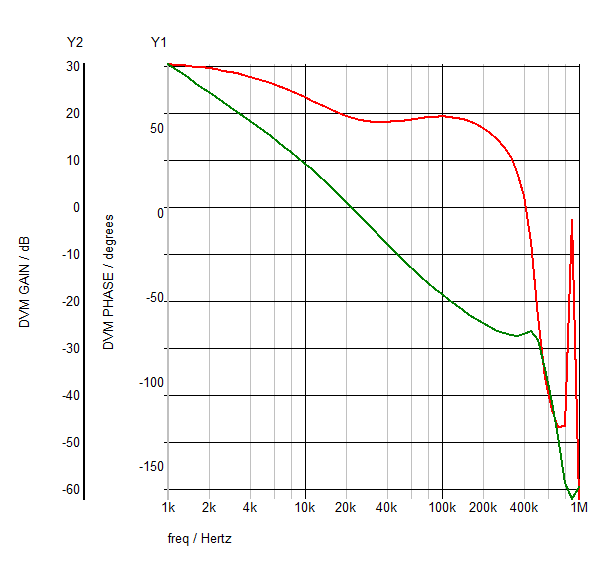

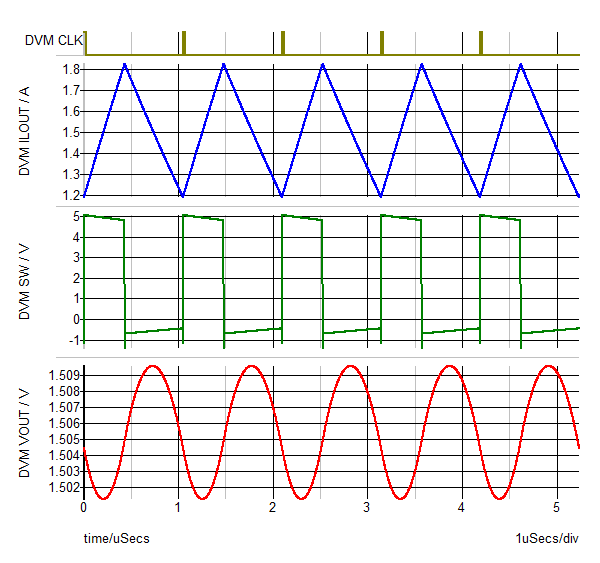

| ILOAD | AVG 1.50063 MIN 1.49625 MAX 1.50451 RMS 1.50063 PK2PK 8.25515m |

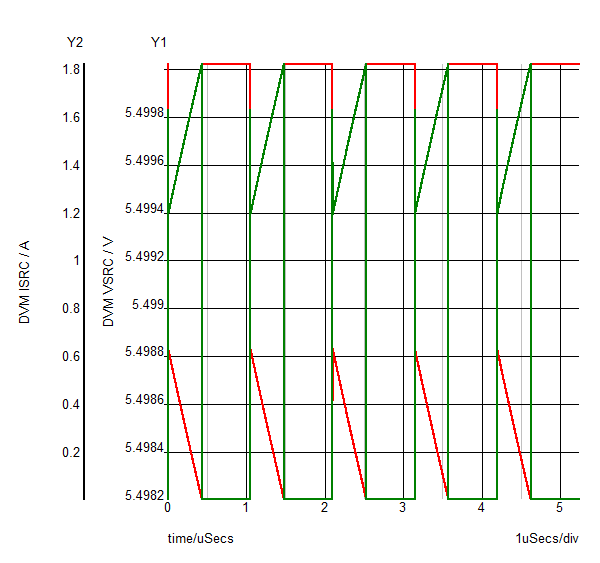

| ISRC | AVG 619.346m MIN 466.026u MAX 1.81961 RMS 973.383m PK2PK 1.81914 |

| min_phase | 56.1713 |

| min_phase_freq | 21.6616k |

| phase_crossover_freq | 417.534k |

| phase_margin | 56.0928 |

| Power(LOAD) | 2.25938 |

| Power(SRC) | 3.40545 |

| VLOAD | AVG 1.50562 MIN 1.50123 MAX 1.50951 RMS 1.50562 PK2PK 8.28261m |

| VSRC | AVG 5.49938 MIN 5.49818 MAX 5.5 RMS 5.49938 PK2PK 1.81914m |

| Measured Spec Values | |

| Max_VLOAD | PASS: Max. Output1 Voltage (1.50951) is less than or equal to Max. Output1 Voltage Spec (1.58025) |

| Min_VLOAD | PASS: Min. Output1 Voltage (1.50123) is greater than or equal to Min. Output1 Voltage Spec (1.42975) |

| min_gain_margin | PASS: Gain Margin (26.8904) is greater than Min. Gain Margin (12) |

| min_phase_margin | PASS: Phase Margin (56.0928) is greater than Min. Phase Margin (35) |

Bode Plot

GAIN

PHASE

|

|

| SXGPH File | simplis_ac1_36.sxgph |

LOAD

VLOAD

ILOAD

|

|

| SXGPH File | simplis_pop1_19.sxgph |

SRC

VSRC

ISRC

|

|

| SXGPH File | simplis_pop1_9.sxgph |

E/A Gain and Phase

Error Amplifier Gain

Error Amplifier Phase

|

|

| SXGPH File | simplis_ac1_43.sxgph |

default

CLK

ILOUT

SW

VOUT

|

|

| SXGPH File | simplis_pop1_14.sxgph |

| Other SXGPH Files | |

| clock#pop | simplis_pop1_1.sxgph |