Advanced SIMPLIS Training

|

To download the examples for Module 2, click Module_2_Examples.zip

In this Topic Hide

The Core POP Process recursively calculates and refines the initial conditions of the system, causing the circuit to reach steady-state much faster than running a long transient.

The details of a "pass" through the Core POP Process.

The progress of a POP analysis can be output to the graph viewer by checking the Output POP progress check box on the POP Advanced Options dialog.

Open the schematic 2.7_SelfOscillatingConverter_POP.sxsch.

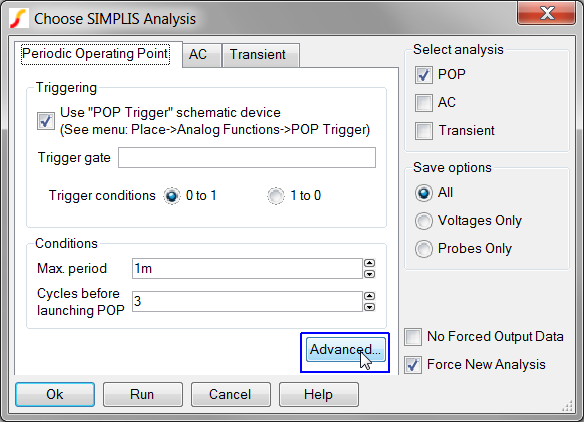

From the schematic menu, select Simulator

Choose Analysis...

menu option. The training material shortcut F8

will execute this menu item.

Result: The Choose Analysis dialog

opens to the POP tab.

Click on the Advanced...

button to open the POP Advanced Options dialog.

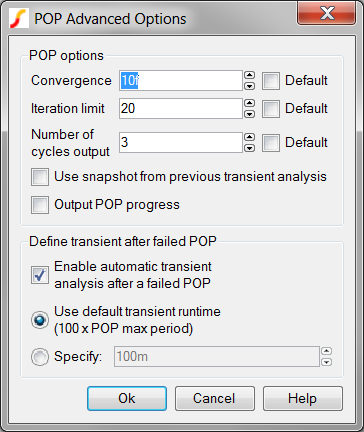

Result: The POP Advanced Options dialog

opens:

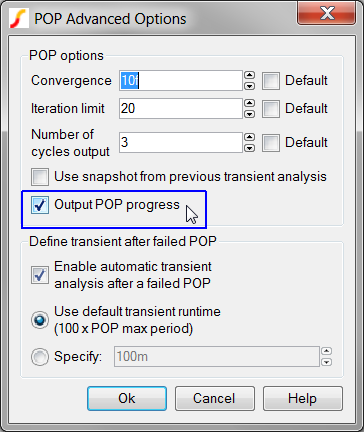

Check the Output POP progress

check box. The dialog should now appear as follows:

Click the Ok button on the POP Advanced Options dialog.

Click the Run button

on the Choose SIMPLIS Analysis dialog.

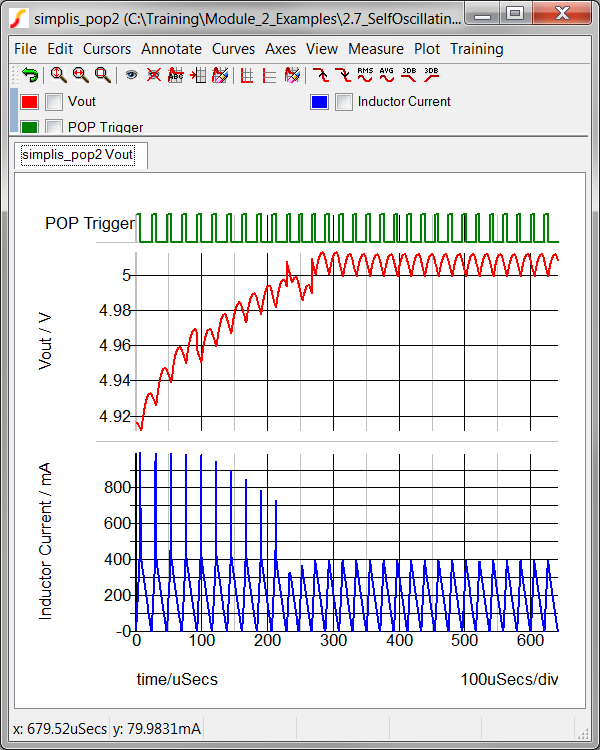

Result: The POP simulation starts and as

the simulation progresses, the output voltage waveform, Vout,

has vertical discontinuities, or jumps, where the Core POP Process

predicts and sets the initial conditions of the circuit.

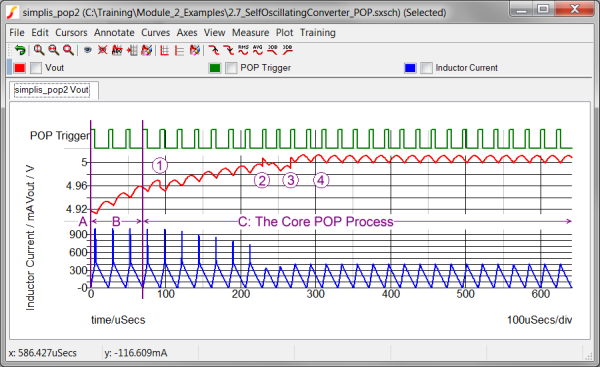

In the previous topic, 2.3.1 Overview of the POP Analysis, the POP Analysis was divided into four phases, labeled A-D. In the simulation you ran in the Getting Started section of 2.3.1 Overview of the POP Analysis, the graph viewer displayed 3 cycles of steady-state operation from phase D of the POP Analysis. In the getting started step of this topic, you instructed SIMPLIS to show all intermediate simulations which were generated to bring the converter to steady state, that is, all simulation data generated in phases A-C of the POP analysis. Using the same phase notation from the previous topic, a graph annotated with each phase of the POP analysis for this converter is shown below:

In this graph, it is easy to see how the majority of the time spent in the POP Analysis occurs during the Core POP Process. The Core POP Process is a sequence of short transient simulations, where a new set of circuit initial conditions is calculated prior to each transient simulation. In the above graph, the purple numerals 1-4 annotate the first four times that the POP algorithm calculated a new set of initial conditions. Although the circuit initial conditions are recursively calculated and set at the beginning of each pass through the POP Process, the changes for the remaining POP passes are so small that they cannot be visually detected on the graph. Each of these initial condition reset events initiates a pass through the Core POP Process.

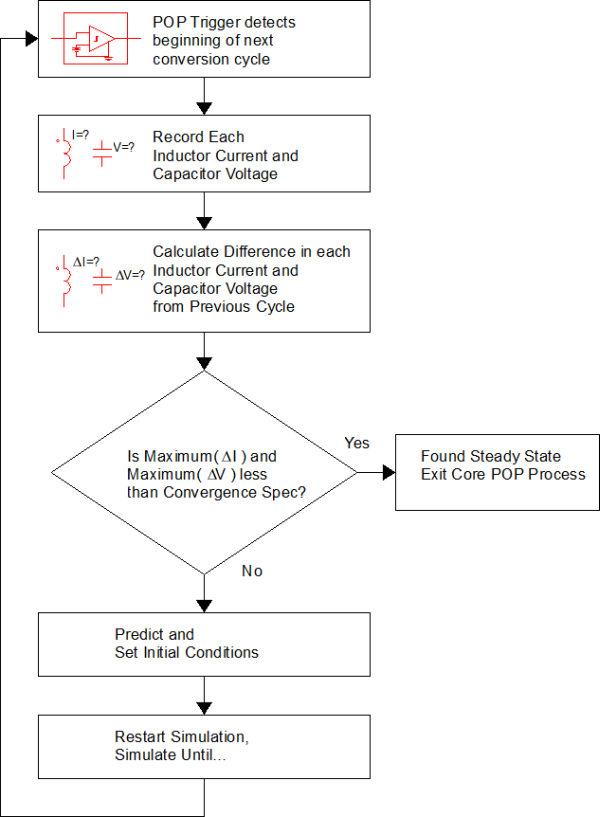

The Core POP Process is essentially a software control loop applied to your circuit. As such, the Core POP Process can be described with the flow chart below. In this flow chart, each POP "Pass" or interation represents a complete loop through the flow chart. When the circuit reaches steady-state, the Core POP Process is exited and the simulator generates the Number of cycles output from Phase D of the POP Analysis described in 2.3.1 Overview of the POP Analysis.

Note: The number of actual switching cycles simulated per pass through the POP Process is variable.

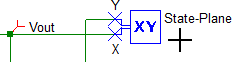

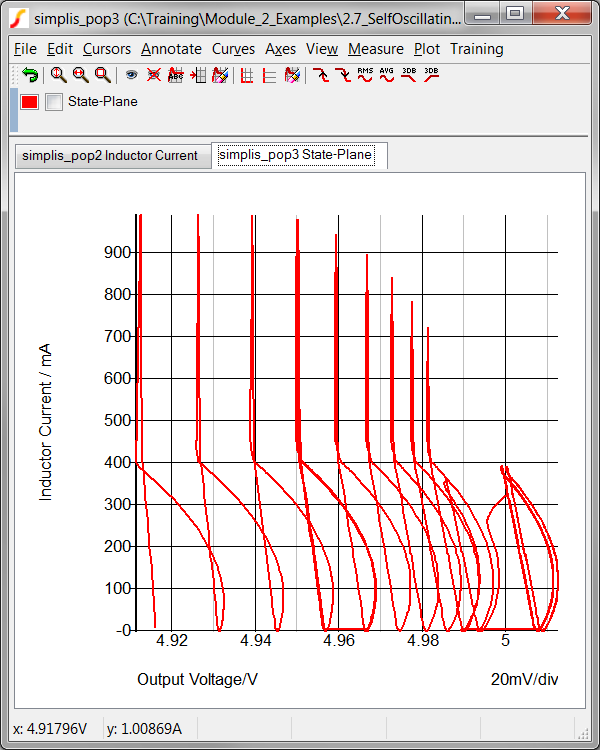

The flyback converter used in example 2.7_SelfOscillatingConverter_POP.sxsch has two main energy storage elements, the magnetizing inductance L4, and the output capacitance C1. A state plane plot is nothing more than a x-y plot of the inductor current vs. the capacitor voltage. The state plane plot of the two main energy storage elements of the converter is often useful to visualize the response of the converter. In the next exercise, you will output a state plane plot for the converter.

Close the graph viewer.

On the upper right hand corner of the schematic find the XY

probe connected to the output:

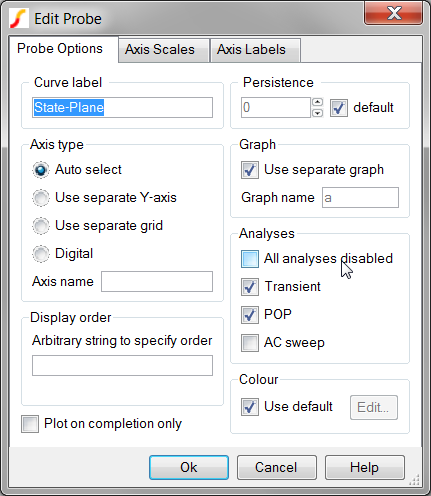

Double click on the probe to open the Edit Probe dialog. Un-check

the All analyses disabled

check box as show below:

Result: Both the POP and Transient analysis

check boxes will be checked.

Click Ok to accept the Edit Probe dialog changes.

Run the simulation.

Result: The simulation executes as before,

showing the POP progress. After the simulation completes, the x-y

state plane plot is generated.

Notice that the time variable doesn't appear in the state plane plot. To better visualize how the converter enters into steady state, you have taken the same simulation results and overlaid green curves representing the different passes through the Core POP Process. In the animated GIF image below, the actual simulated output voltage and magnetizing current, as well as the state plane plot are plotted.

The following slideshow illustrates the sequence of actions that occur during a POP analysis.

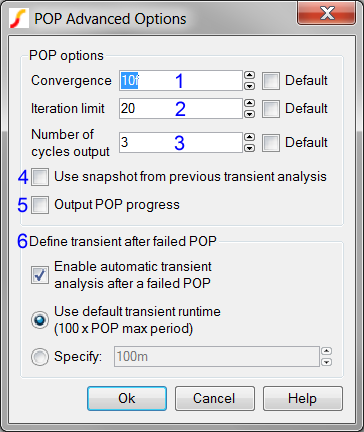

Most parameters for the Core POP Process are set on the POP Advanced

Options dialog, shown below with annotations:

|

1: The maximum change in any state element when the circuit is in steady-state. |

| 2: The maximum number of passes through the Core POP Process. | |

| 3: The number of steady-state cycles to output to the graph viewer. | |

| 4: If checked, the POP analysis will start using a snapshot from a previous transient analysis. | |

| 5: If checked, the graph will display the POP Progress instead of the steady-state Number of cycles output. | |

| 6: Determines the behavior if the POP analysis

fails.

|

◀ 2.3.1 Overview of the Periodic Operating Point (POP) Analysis |

© 2015 simplistechnologies.com | All Rights Reserved