|

In this Topic Hide

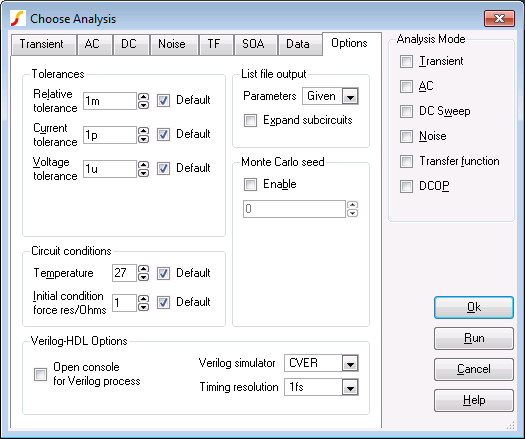

The simulator features a large number of option settings although, fortunately, the vast majority can be left at their default values for nearly all applications. A few option settings can be set via the Choose Analysis dialog box and these are described in the following sections. The remainder can be controlled using the simulator's .OPTIONS control details of which may be found in the Simulator Reference Manual/Command Reference/.OPTIONS.

Note that the Verilog-HDL group will only be displayed in versions with the Verilog-HDL feature

| Relative Tolerance |

Controls the overall accuracy of the simulation. The default value is 0.001 and this is adequate for most applications. If you are simulating oscillator circuits it is recommended to reduce this to 0.0001 or lower.

Increasing this value will speed up the simulation but often degrades accuracy to an unacceptable level. |

| Current Tolerance | Sets the minimum tolerance for current. It may be beneficial to increase this for circuits with large currents. |

| Voltage Tolerance | Sets the minimum tolerance for voltage. It may be beneficial to increase this for circuits with large voltages. |

| Temperature | Circuit temperature in $°C$. |

| Initial Condition Force Resistance | Initial conditions apply a voltage to a selected node with a force resistance that defaults to $1\Omega$. This option allows that force resistance to be changed. |

| Expand subcircuits | If checked, the listing of expanded subcircuits will be output to the list file. This is sometime useful for diagnosing problems. | |||||||

| Parameters |

Controls the level of model and device parameter output to the list file. Options are:

|

Seed for pseudo random number generator used to generate random numbers for tolerances. See Multi-step Analyses. If Enable check box is unchecked, a seed value will be chosen by the simulator.

This section will only show if Verilog-HDL simulation is available for your version of SIMetrix.

| Open console for Verilog process | When the Verilog simulator runs, a console window will be displayed showing any output messages from the simulator. See Open Console for Verilog Process for details. |

| Verilog simulator | Simulator that will be used to run Verilog-HDL. See Verilog Simulator for details. |

| Timing resolution | Time resolution in Verilog simulator. See Timing Resolution for details. |

|