DVM - Design Verification Module

|

The Ramp Load subcircuit models a single, non-repeating ramp or step in load current using a resistor and a PWL current source.

The Ramp Load subcircuit is used in the StepLoad() test objective. You can change any managed DVM load to use the Ramp Load by entering a Ramp() entry in the Load column.

Other similar loads include the following:

In this Topic Hide

The table below explains the parameters used in the Ramp Load subcircuit.

| Parameter Name | Default | Data Type | Range | Units | Parameter Description |

FINAL_CURRENT |

750m | Real | min: 0 | A | The final current for the PWL current source portion of the load. The Ramp Load continues at this current for all simulation times greater than TIME_DELAY + RISE_TIME. This can be a numeric value or a symbolic value, such as a percentage of full load. |

LOAD_NAME |

LOAD | String | n/a | n/a | Name of the DVM load. This name cannot contain spaces. |

LOAD_RESISTANCE |

2.00667 | Real | min: 0 | Ω | The resistance value which models the starting current of the load |

RISE_TIME |

100u | Real | min: 0 | s | The ramp rise time in seconds |

START_CURRENT |

0 | Real | min: 0 | A | The starting current for the PWL current source portion of the load. This is typically set to 0 since the minimum load current is modeled with the LOAD_RESISTANCE parameter. This can be a numeric value or a symbolic value, such as a percentage of full load. |

TIME_DELAY |

10u | Real | min: 0 | s | The time delay before the ramp initiates |

To set any managed DVM load to a Ramp Load subcircuit, place a Ramp() testplan entry in the Load column.

The Ramp() testplan entry has the following syntax with the arguments explained in the table below.

Ramp(REF, ISTART, IFINAL)

Ramp(REF, ISTART, IFINAL, OPTIONAL_PARAMETER_STRING)

| Argument | Range | Description |

REF |

n/a |

The actual reference designator of the DVM load or the more generic syntax of OUTPUT:n where n is an integer indicating a position in the list of managed DVM loads. |

ISTART |

min: 0 |

The starting current for the load. This can be a numeric value or a symbolic value, such as percentage of full load. |

IFINAL |

min: 0 |

The final current for the load. This can be a numeric value or a symbolic value, such as a percentage of full load. |

OPTIONAL_PARAMETER_STRING |

n/a |

Parameter string with timing parameters TIME_DELAY and/or RISE_TIME* |

* If both parameters are specified, join the two parameter key-value pairs with a space, as shown in the example below. The order of the parameter names does not matter.

DVM calculates the LOAD_RESISTANCE parameter from the $I_{START}$ argument and subtracts the equivalent starting current from the PWL portion of the load. The calculation for the LOAD_RESISTANCE parameter is based on the following:

Note: If the specified starting current is 0 and the load is configured by DVM using either a Ramp() function or the StepLoad() test objective, DVM replaces the Ramp Load subcircuit with a Ramp Pure Load subcircuit. The Ramp Pure Load does not use a parallel resistance to model the starting current.

During a StepLoad() test, DVM sets the output under test to use the Ramp Load subcircuit. Then DVM sets the TIME_DELAY and RISE_TIME parameters for the Ramp Load. You can change the timing with the Ramp() function call by providing the timing parameters as an optional parameter string, which is the fourth argument to the Ramp() function call.

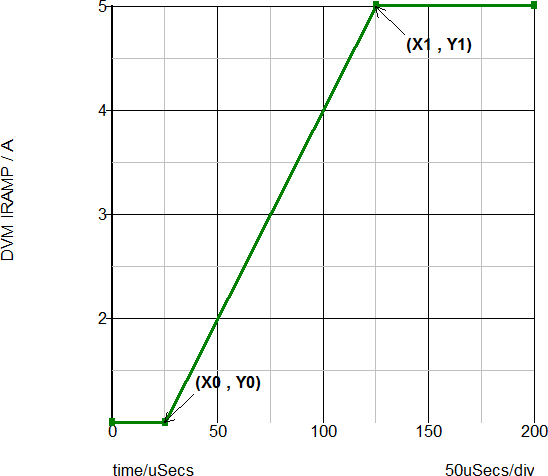

The following example sets the first DVM managed load to a Ramp Load with a starting current of 1A and a final current of 5A.

Note:In this example, the Load column is the first column in the testplan and, therefore, begins with the special three character sequence: *?@.

| *?@ Load | ||||

|---|---|---|---|---|

| Ramp(OUTPUT:1, 1, 5, TIME_DELAY=25u RISE_TIME=100u) | ||||

The results of this testplan entry are shown below:

| Annotation | Value |

| X0 | TIME_DELAY |

| X1 | TIME_DELAY + RISE_TIME |

| Y0 | ISTART (see note below) |

| Y1 | IFINAL (see note below) |

Note: The actual load current depends on the LOAD_RESISTANCE parameter and the actual time-varying load voltage. The ISTART current is modeled by a resistor with a resistance equal to the value of LOAD_RESISTANCE . The PWL current source has points defined by the START_CURRENT and FINAL_CURRENT parameter values.

© 2015 simplistechnologies.com | All Rights Reserved