DVM - Design Verification Module

|

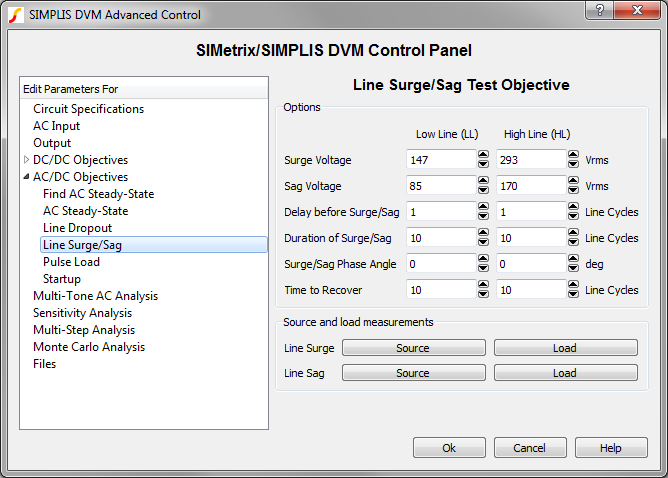

The purpose of the LineSag() test is to determine the converter response to a sudden decrease in line voltage amplitude. The input is configured as a AC Line Surge/Sag Input Source, and the output is configured as a Resistive Load. The initial conditions for the simulation are typically found with a FindAcSteadyState() test, which runs a long transient simulation and saves the initial conditions using the GenerateInitFile testplan entry.

The LineSag() test objective runs a transient simulation on the converter

with the timing based on values entered in the Line

Surge/Sag page, which is shown below and accessed from the Full Power

Assist DVM control symbol.

This test objective measures the following scalar values:

Percentage change in output load voltages over the final two line cycles

In this Topic Hide

The LineSag() function has the following syntax with the arguments described in the table below:

LineSag(REF, LINE_RANGE, NOMINAL_VOLTAGE,

SAG_VOLTAGE,

FREQUENCY)

LineSag(REF, LINE_RANGE, NOMINAL_VOLTAGE,

SAG_VOLTAGE,

FREQUENCY, OPTIONAL_PARAMETER_STRING)

| Argument | Range | Description |

| REF | n/a | The actual reference designator of the DVM Source or the generic syntax of INPUT:n where n is an integer indicating a position in the list of managed DVM sources. |

| LINE_RANGE | LL or HL | The line range to select the correct symbolic voltage value. This can only be the two strings LL or HL. |

| NOMINAL_VOLTAGE | min:0 | The RMS voltage for the input source during the normal operating conditions. The voltage can be a numeric value or a symbolic value, such as a percentage of nominal input voltage. Symbolic values use the LINE_RANGE parameter to find the correct symbolic value. |

| SAG_VOLTAGE | min:0 | The RMS voltage for the input source during the sag event. The voltage can be a numeric value or a symbolic value, such as HL_Surge. Symbolic values use the LINE_RANGE parameter to find the correct symbolic value. |

| FREQUENCY | min: > 0 | The AC line frequency of the input source. This is used to both set the frequency of the input source and to set the simulation timing. The frequency can be a numeric or a symbolic value, such as F_High or F_Low. |

| OPTIONAL_PARAMETER_STRING | n/a | Parameter string with a combination of one

or more timing parameters:

|

* If more than one parameter is specified, join the parameter key-value pairs with a space, as shown in the example below. The order of the parameter names does not matter.

DVM sets the timing parameters for the LineSag() test objective based on values that you enter on the Line Surge/Sag page of the DVM Full Power Assist control symbol:

Delay Before Surge/Sag, Duration of Surge/Sag, Time to Recover, and Surge/Sag Phase Angle.

In the OPTIONAL_PARAMETER_STRING and in the calculations below, these values are renamed as follows:

The time delay is based on the following conditions and calculations. Typically the LINE_PHASEANGLE is set to 0, although in a 3 phase system only one of the three line sources will have a zero LINE_PHASEANGLE.

If LINE_PHASEANGLE is greater than 0, then

\[ \text{TIME_DELAY} = \frac{360 - \text{LINE_PHASEANGLE}}{360 * \text{FREQUENCY}} + \frac{\text{NCYLES1}}{\text{FREQUENCY}} + \frac{\text{PHASE_ANGLE}}{360 * \text{ FREQUENCY}} \]

If LINE_PHASEANGLE is less than or equal to 0, then

\[ \text{TIME_DELAY} = \frac{\text{NCYLES1}}{\text{FREQUENCY}} + \frac{\text{PHASE_ANGLE}}{\text{360} * \text{FREQUENCY}} \]

The pulse width and stop time are based on these calculations:

\[ \text{PULSE_WIDTH} = \frac{\text{NCYLES2}}{\text{FREQUENCY}} \]

\[ \text{STOP_TIME} = \frac{\text{NCYCLES1} + \text{NCYCLES2} + \text{NCYCLES3}}{\text{FREQUENCY}}\]

A special note about the input voltage source used for this test objective. The slew rate of the input line voltage during the line transitions is limited by the input source. Each AC source has a programmable filter and slew rate limiter - the combination of these two circuits will limit the rate of change of the input line voltage. Of course, if the sag phase angle is set to 0, 180 or 360, there is no instantaneous change in the input voltage, as the line source changes when the line voltage is zero.

The LineSag() test objective sets the source and load subcircuits to the following:

| Source | Control Source (if used) | Load |

| AC Line Surge/Sag Input Source | DC Auxiliary Source | Resistive Load |

Loads other than the output under test are set to the Resistive Load. All other sources are set to either the DC Input Source for DC sources or the AC Fixed Input Source for the AC input sources.

The LineSag() test objective measures the following scalar values where {load_name} is the name assigned to each load, and {source_name} is the name assigned to each source.

| Scalar Name | Description |

| Frequency({source_name}) | A number which represents the line frequency. |

| V{load_name}%_diff_last_2_linecycles | The percent change in the output voltage when averaged over the last two line cycles. |

| vout{n}_recovery_time | The time required for the output voltage to reach the output voltage regulation band after the line sag event. |

| I{source_name} | Minimum, Maximum, and RMS values of the source current during the entire simulation time. |

| I{source_name} During Sag | Maximum and RMS values of the source current during the sag event. |

| I{source_name} Inrush Current | The maximum current for the input source after the line sag event. |

| I{load_name} | Minimum and Maximum values of the load current. |

| V{source_name} | Minimum and Maximum values of the source voltage. |

| V{source_name} After Sag | The RMS voltage of the source after the sag event. |

| V{source_name} During Sag | The RMS voltage of the source during the sag event.. |

| V{load_name} | Minimum and Maximum values of the load voltage during the entire simulation time. |

| V{load_name} During Sag | Minimum value of the load voltage during the sag event. |

| V{load_name} At Simulation Start Time | The output voltage taken at time=0. |

| V{load_name} Last LineCycle | The average value of the output voltage during the last line cycle in the simulation. Used for the V{load_name}%_diff_last_2_linecycles calculation. |

| V{load_name} Previous LineCycle | The average value of the output voltage during the second to the last line cycle in the simulation. Used for the V{load_name}%_diff_last_2_linecycles calculation. |

| V{load_name} overshoot | Maximum value of the load voltage during the sag event. |

In the following table, {load_name} is the name assigned to each load, and {source_name} is the name assigned to each source.

| Scalar Name | PASS/FAIL Criteria |

| AC_Settling({load_name}) | The percentage change in the output load voltage over the final two line frequency cycles is less than the maximum specification value. |

| Max_I{load_name}_Inrush | The converter passes if the maximum source current is less than the maximum source current inrush specification. |

| Min_V{load_name} | The minimum value of the output during the simulation time is greater than the minimum specification value. |

| Max_V{load_name} | The maximum value of the output during the simulation time is less than the maximum specification value. |

| Max_V{load_name}_overshoot | The maximum overshoot value of the output during the simulation time is less than the overshoot specification value. |

An example of the LineSag() test objective taken from the AC/DC (1-input/1-output) testplan is shown below. This test objective configures the load to sag between the LL_Nominal and LL_Sag symbolic values. Both values are defined on the Line Surge/Sag page of the Full Power Assist DVM control symbol. The timing of the line sag event will be determined by the values on the same page.

| *?@ Analysis | Objective | Source | Load | Label | GenerateInitFile | IncludeInitFile |

| Transient | LineSag(INPUT:1, LL, Nominal, LL_Sag, F_High) | Load(OUTPUT:1, 100%) | Transient|LineSag|LL_Nominal_to_LL_Sag|F_High|100% Load | INITFILE_LL_Nominal_F_High_100% Load |

The following LineSag() test objective uses the OPTIONAL_PARAMETER_STRING argument to set the line voltage to sag between the LL_Nominal and LL_Sag symbolic values and sets the time delay before the sag (NCYLES1) to 2 line cycles, and the sag duration to 10 line cycles.

LineSag(INPUT:1, HL, HL_Maximum, HL_Surge, F_Low, NCYCLES1=2 NCYCLES2=10)

You can view the complete test report in a new browser window here: LineSag() Test Report. Below is an interactive link to the same test report.

© 2015 simplistechnologies.com | All Rights Reserved