Analog-to-Digital Converter w/ Adjustable Voltage Reference

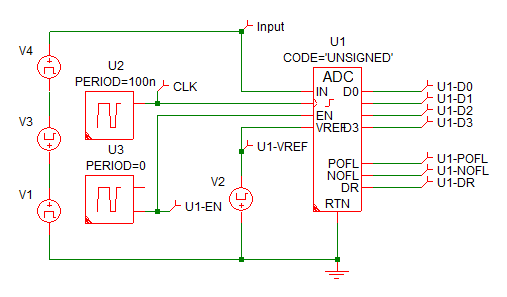

The Analog-to-Digital Converter w/ Adjustable Voltage Reference models a generic flash-type ADC.

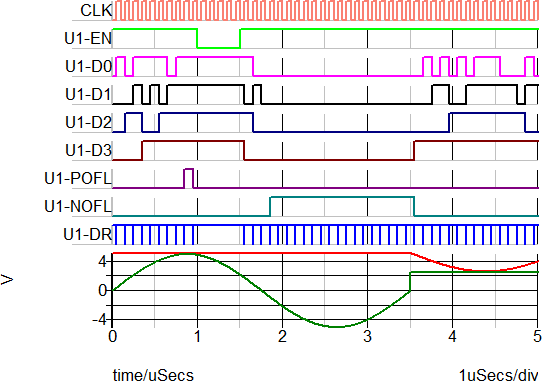

- The ADC starts the conversion at the rising or falling edge of the clock, depending on the selected value of the Trigger Condition.

- The sampling of the analog input signal begins at this point and is complete after the interval specified by Sample delay.

- The output data changes in response to the clock trigger event, which occurs after the number of seconds specified by Convert Time.

- At the same time that the output initially changes, the Data Ready output goes low (inactive) and then high again after a delay equal to Data Ready delay.

This model has an adjustable voltage reference. For an analog-to-digital converter with a fixed voltage reference, see Analog-to-Digital Converter.

In this topic:

| Model Name: | Analog-to-Digital Converter w/ Adjustable Voltage Reference | |||

| Simulator: |  |

This device is compatible with the SIMPLIS simulator. | ||

| Parts Selector Menu Location: | ||||

| Symbol Library: | None - the symbol is automatically generated when placed or edited. | |||

| Model Library: | None - the model is automatically generated when the simulation is run. | |||

| Subcircuit Name: | SIMPLIS_DIGI1_D_A2D_AVREF_CONVERTER_Y | |||

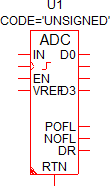

| Symbol: |

|

|||

| Multiple Selections: | Only one device at a time can be edited. | |||

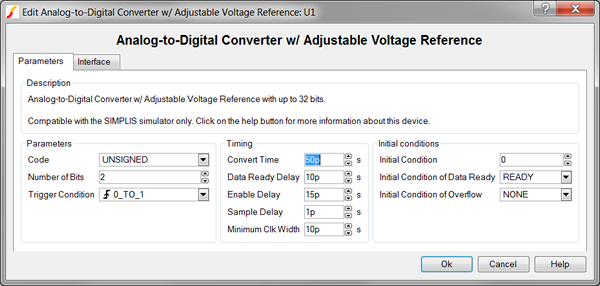

Editing the Analog-to-Digital Converter w/ Adjustable Voltage Reference

To configure the Analog-to-Digital Converter w/ Adjustable Voltage Reference, follow these steps:

- Double click the symbol on the schematic to open the editing dialog to the Parameters tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description | ||||||||||||

| Code | Encoding scheme for binary outputs of the ADC | ||||||||||||

| Number of Bits | Number of output bits for this Analog-to-Digital Converter w/ Adjustable Voltage Reference | ||||||||||||

| Trigger Condition | Determines the

triggering condition of the ADC clock pin:

|

||||||||||||

| Convert Time | Time required to convert analog input to digital output | ||||||||||||

| Data Ready Delay | Delay from when the ADC output changes until the data-ready signal is true | ||||||||||||

| Enable Delay | Delay from when the enable pin goes active until the output is enabled | ||||||||||||

| Sample Delay | Time required to sample the analog input | ||||||||||||

| Minimum Clk Width | Minimum valid clock width. Clock widths less than this parameter will not trigger the ADC. | ||||||||||||

| Initial Condition | Initial condition of the ADC converter output in decimal notation at t=0 | ||||||||||||

| Initial Condition of Data Ready | Initial condition of the data ready output of the ADC | ||||||||||||

| Initial Condition of Overflow | Initial condition of

the overflow outputs of the ADC:

|

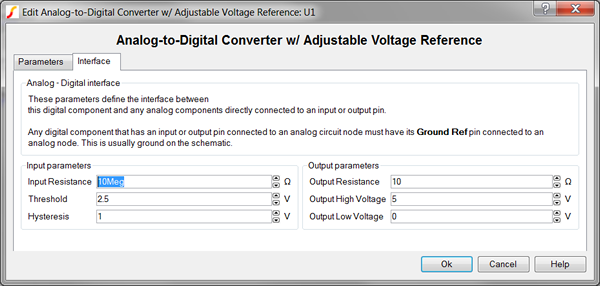

To define the parameters for the interface between this digital component and each analog component connected directly to an input or output pin, follow these steps:

- From the Edit Analog-to-Digital Converter w/ Adjustable Voltage Reference dialog box, click on the Interface tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description | |||||||

| Input Resistance | Input resistance of each ADC input pin | |||||||

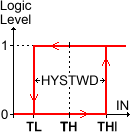

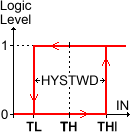

| Hysteresis, Threshold |  |

Hysteresis and

Threshold of the inputs. The hysteretic-window width, HYSTWD

is centered around Threshold (TH) voltage. To

determine the actual threshold ( TL , THI ),

substitute Threshold (TH) and Hysteresis

(HYSTWD) in each of the following formulas:

|

||||||

| Output Resistance | Output resistance of each ADC output pin | |||||||

| Output High Voltage | Output high voltage for each ADC output pin | |||||||

| Output Low Voltage | Output high voltage for each ADC output pin | |||||||

Examples

The test circuit used to generate the waveform examples in the next section can be downloaded here: simplis_061_adc_w_adj_v_ref_example.sxsch.

Waveforms

Subcircuit Parameters

Because the Analog-to-Digital Converter w/ Adjustable Voltage Reference model is generated by a template script when the simulation is executed, a hand-coded model cannot be inserted into a netlist. The template script for this device is simplis_make_a2d_model.sxscr, which licensed users can download as part of a zip archive of all built-in scripts.

To download the zip archive, follow these steps:

- Click http://www.simetrix.co.uk/simetrix80/scripts.zip to download the script archive.

- Enter the user name and password you received with your license file.

The following parameter table defines the parameters used in this model.

| Parameter Name | Label | Data Type | Range | Units | Parameter Description | |||||||||||||

| CODE | Code | String |

|

none | Encoding scheme for binary outputs of the ADC | |||||||||||||

| CONVERT_TIME | Convert Time | Number | any | s | Time required to convert analog input to digital output | |||||||||||||

| DATA_READY_DELAY | Data Ready Delay | Number | any | s | Delay from when the ADC output changes until the data-ready signal is true | |||||||||||||

| ENABLE_DELAY | Enable Delay | Number | any | s | Delay from when the enable pin goes active until the output is enabled | |||||||||||||

| HYSTWD, TH |

Hysteresis, Threshold |

Number | min: 1f | V |  |

Hysteresis and Threshold of

the inputs. The hysteretic-window width, HYSTWD is centered around

Threshold (TH) voltage. To determine the actual threshold (

TL , THI ), substitute Threshold (TH) and

Hysteresis (HYSTWD) in each of the following formulas:

|

||||||||||||

| IC | Initial Condition | Number |

|

none | Initial condition of the ADC converter output in decimal notation at t=0 | |||||||||||||

| IC_DATA_READY | Initial Condition of Data Ready | String |

|

none | Initial condition of the data ready output of the ADC | |||||||||||||

| IC_OFL | Initial Condition of Overflow | String |

|

none | Initial condition of the

overflow outputs of the ADC:

|

|||||||||||||

| MIN_CLK | Minimum Clk Width | Number | 1f to 1024 | s | Minimum valid clock width. Clock widths less than this parameter will not trigger the ADC. | |||||||||||||

| NUMBITS | Number of Bits | Integer | none | Number of output bits for this Analog-to-Digital Converter w/ Adjustable Voltage Reference | ||||||||||||||

| RIN | Input Resistance | Number | min: 100 | Ω | Input resistance of each ADC input pin | |||||||||||||

| ROUT | Output Resistance | Number | min: 1m | Ω | Output resistance of each ADC output pin | |||||||||||||

| SAMPLE_DELAY | Sample Delay | Number | any | s | Time required to sample the analog input | |||||||||||||

| TRIG_COND | Trigger Condition | String |

|

none | Determines the triggering

condition of the ADC clock pin:

|

|||||||||||||

| VOH | Output High Voltage | Number | any | V | Output high voltage for each ADC output pin | |||||||||||||

| VOL | Output Low Voltage | Number | any | V | Output high voltage for each ADC output pin | |||||||||||||