Digital Device Overview

In this topic:

Common Parameters

A number of model parameters are common to most of the digital models. These are described below.

Family Parameters

These identify the logic family to which the input and outputs belong. See Logic families for a detailed explanation. Most models have three family parameters:

| Family name | Description |

| in_family | Specifies family for inputs. If omitted, the input family is specified by the FAMILY parameter |

| out_family | Specifies family for outputs. If omitted, the output family is specified by the FAMILY parameter |

| family | Default value for IN_FAMILY and OUT_FAMILY |

Output Parameters

| Parameter name | Description |

| out_res | This is used to calculate loading delay. It has dimensions of Ohms so is referred to as a resistance. The additional loading delay is calculated by multiplying OUT_RES by the total capacitative load detected on the node to which the output connects. |

| min_sink | Used to calculate static loading effects. This is the current that the device is able to sink. Current flowing out of the pin is positive so this parameter is usually negative. If the total sink load current is arithmetically smaller (i.e. more negative) than this parameter then the output will be forced to an UNKNOWN state. This is used to implement fan out limitations in bipolar logic. |

| max_source | Used to calculate static loading effects. This is the current that the device is able to source. Current flowing out of the pin is positive. If the total source load current is larger than this parameter then the output will be forced to an UNKNOWN state. This is used to implement fan out limitations in bipolar logic. |

Input Parameters

| Parameter name | Description |

| sink_current | Current that the input sinks. Positive current flows into the device so this parameter is usually negative. The total of all the input sink currents are added together when a node is in the logic '0' state. If the total sink load current is arithmetically smaller (i.e. more negative) than the MIN_SINK parameter of the device driving the node, then it will be forced to an UNKNOWN state. This is used to implement fan out limitations in bipolar logic. |

| source_current | Current that the input sources. Positive current flows into the device. The total of all the input source currents are added together when a node is in the logic '1' state. If the total source load current is larger than the MAX_SOURCE parameter of the device driving the node, then it will be forced to an UNKNOWN state. This is used to implement fan out limitations in bipolar logic. |

Delays

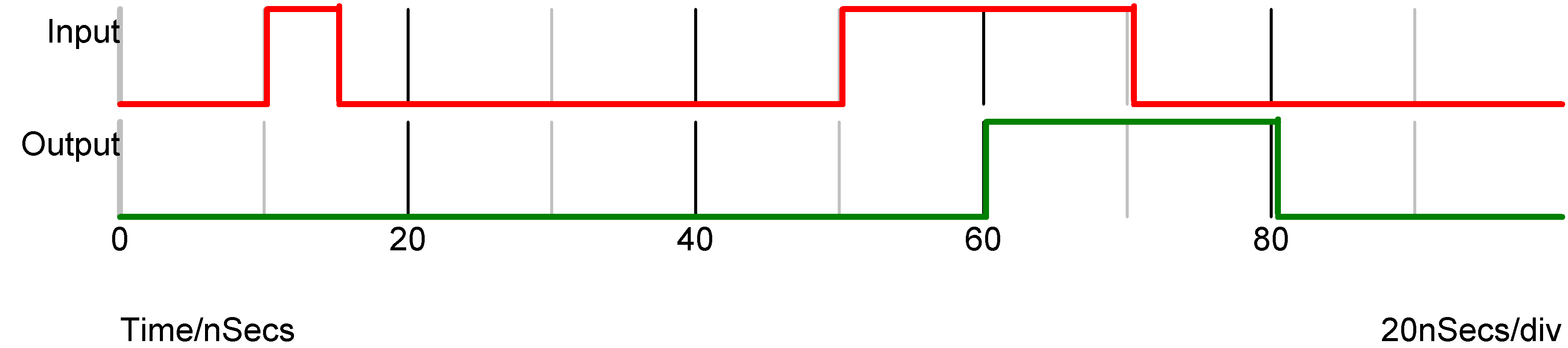

Most digital devices have at least one model parameter that specifies a time delay. Unless otherwise noted, all delays are inertial. This means that glitches shorter than the delay time will be swallowed and not passed on. For example, the following waveforms show the input and output of a gate that has a propagation delay of 10nS. The first pulse is only 5nS so does not appear at the output. The second pulse is 20nS so therefore is present at the output delayed by 10nS.

The Buffer device has an optional stored delay (also known as transport delay) parameter that makes possible the specification of pure delays.

| ◄ NXP Compact Models | And Gate ▶ |