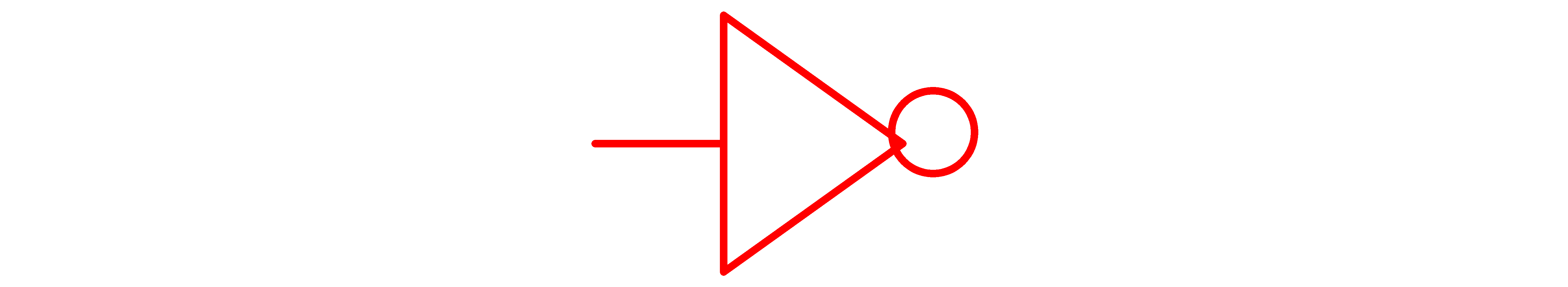

Inverter

In this topic:

Netlist entry

Axxxx in out model_name

Connection details

| Name | Description | Flow | Type |

| in | Input | in | d |

| out | Output | out | d |

Model format

.MODEL model_name d_inverter parameters

Model parameters

| Name | Description | Type | Default | Limits |

| rise_delay | Rise delay | real | 1nS | 1e-12 ???MATH???- \infty???MATH??? |

| fall_delay | Fall delay | real | 1nS | 1e-12 ???MATH???- \infty???MATH??? |

| input_load | Input load value (F) | real | 1pF | none |

| family | Logic family | string | HC | none |

| in_family | Input logic family | string | UNIV | none |

| out_family | Output logic family | string | UNIV | none |

| out_res | Digital output resistance | real | 100 | ???MATH???0 - \infty???MATH??? |

| out_res_pos | Digital output res. pos. slope | real | out_res | ???MATH???0 - \infty???MATH??? |

| out_res_neg | Digital output res. neg. slope | out_res | ???MATH???0 - \infty???MATH??? | |

| open_c | Open collector output | boolean | FALSE | none |

| min_sink | Minimum sink current | real | -0.001 | none |

| max_source | Maximum source current | real | 0.001 | none |

| sink_current | Input sink current | real | 0 | none |

| source_current | Input source current | real | 0 | none |

Device Operation

If the OPEN_C parameter is not specified or is FALSE, this device simply inverts the state of its input. I.e. if the input is logic '0' the output will be logic '1' and vice-versa. If the input is UNKNOWN the output will also be UNKNOWN.

If OPEN_C is TRUE, the output state is always at logic '0' and the input determines its strength. If the input is at logic '1' the output strength is STRONG and if it is at logic '0' the output strength is HI-IMPEDANCE. The output strength will be UNDETERMINED if the input is UNKNOWN.

| ◄ Digital Signal Source | JK Flip Flop ▶ |