Application A - Create MOSFET Driver Model

A realistic MOSFET driver model in combination with a Level 2 MOSFET model allows you to evaluate the efficiency and switching losses of a switching power supply. This topic describes how to create detailed MOSFET gate driver models in SIMPLIS. After you understand the key concepts of MOSFET driver design, the Application B - Switching Losses and Measuring Efficiency topic explores the applications of MOSFET drivers and how the drive characteristics affect the overall efficiency of the power supply.

To download the examples for the Applications Module, click Applications_Examples.zip

In this topic:

Key Concepts

This topic addresses the following key concepts:

- The output characteristics of a MOSFET driver can be modeled with a PWL resistor.

- Simulation test benches allow you to easily evaluate the performance of a block.

- Using parameterization for the MOSFET driver makes the block reusable.

What You Will Learn

Using the methodology outlined in Module 6, you will create a model for a MOSFET driver that will support the model requirements below.

In this topic, you will learn the following:

- How to use a PWL resistor to model the output characteristics of a driver MOSFET.

- The value of parameterizing a simulation model so that it may be used as a general purpose modeling blocks in future projects.

- The value of characterizing the simulation performance of each SIMPLIS modeling block.

- The importance of creating test benches for each modeling block.

Model Requirements

The MOSFET driver modeling block should do the following:

- Model the losses of a single MOSFET/driver combination including both conduction and switching losses during turn-ON and turn-OFF.

- Parameterize the MOSFET driver model so that it may be used as a general purpose modeling block.

- Isolate the PWM driver input signal from the gate-drive source and sink currents.

- Provide a parameterized asynchronous delay to the PWM input signal, allowing different values for the driver turn-ON delay and turn-OFF delay under no-load conditions.

Model Design Procedure

The design procedure for this model uses the following steps.

- Step 1: Create Model Development Test Bench

- Step 2: Define Detailed Model Requirements

- Step 3: Create Driver Model

- Step 4: Create Driver Test Benches

Step 1: Create Model Development Test Bench

The purpose of a test bench is to create a test environment for efficiently developing a subcircuit simulation model. Eventually, the driver model will be contained within a subcircuit as part of a hierarchical system model. In Module 6, you began developing the load model as a subcircuit. However, with this test bench, you start out developing a driver model in the same flat schematic as in the test bench.

For relatively small but operationally complex circuits, this approach has the advantage of allowing you to see the model being developed at the same hierarchical level as the circuitry which the model interacts with. Once your model is fully tested, you can create a hierarchical model using the same procedure as used in the 5.3 Creating Hierarchical Schematics.

During the development of a single modeling block, the time to move from a flat development test bench to a hierarchical test bench is a judgment call, best determined by the modeler. However, the end product of each functional sub-block model should always be a hierarchical subcircuit. As a general rule, when a functional sub-block model is being characterized and successfully tested against its model requirements, it should already be an appropriately parameterized hierarchical subcircuit. Very large, flat schematics become difficult to manage and are virtually impossible for anyone but the original modeling engineer to understand. After some time passes, even the original engineer will struggle to make sense of how the circuit works.

In order for this driver test bench to support efficient subcircuit development, the test-bench simulations should do the following:

- Run fast

- Exercise the critical driver performance requirements

- Allow incremental development of the driver model

- Facilitate the creation of a subcircuit model

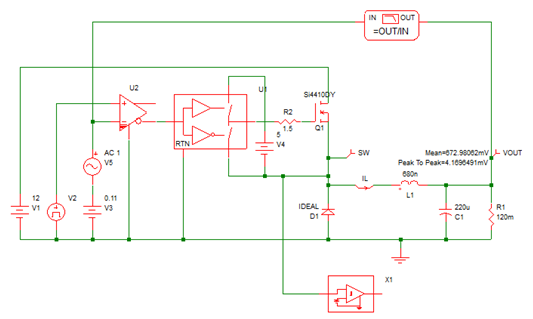

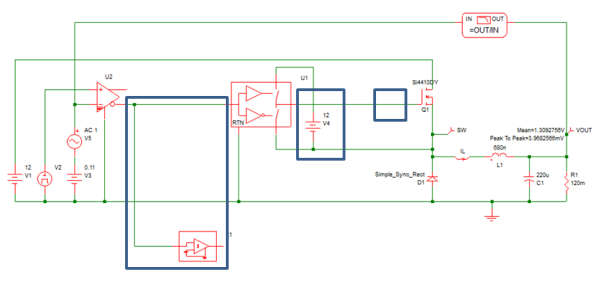

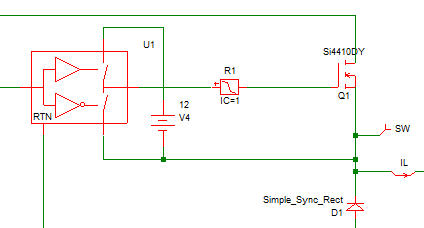

For this example, a simple open-loop Synchronous Buck circuit (apps_a_0_open_loop_buck_converter.sxsch) is used as the foundation of the development test bench.

Further, in this test bench, all attention focuses on the high side MOSFET Q1 and its driver and assumes instantaneous switching for the low side synchronous MOSFET represented by D1.

To modify this schematic to support the development of a MOSFET driver modeling block that will meet the model requirements above, follow these steps:

- To make room for the detailed driver block in the middle, make the changes shown

below.

- Remove gate resistor R2 in series with the gate of Q1.

- Change the value of the voltage on V4 to 12V.

- Move the position of the POP Trigger schematic device to the output of the comparator U2.

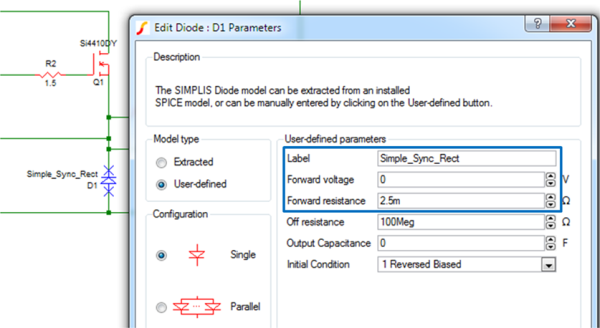

- Change the model of D1 to User-defined with the parameters in the

illustration below:

Result: The schematic should now look like apps_a_1_buck_w_driver_step1.sxsch which you can download here.

Result: The schematic should now look like apps_a_1_buck_w_driver_step1.sxsch which you can download here.

This approach is an effective way to model a synchronous MOSFET when you are not interested in modeling the non-ideal switching behavior of the device. Instead, you have a simple Sync MOSFET model that accurately models the conduction losses; but, because it switches instantaneously, it produces no switching losses in either the high-side or low-side MOSFET. In effect, D1 behaves like a MOSFET with ideal gate-drive waveforms and zero capacitance.

Step 2: Define Detailed Model Requirements

For accurate simulations of a switching power MOSFET, it is essential that both the MOSFET and its drive circuit be well modeled. From earlier discussions in Module 1.0.4 Multi-Level Modeling, you should know that you need at least a Level 2 SIMPLIS MOSFET model to model its switching voltage and current waveforms. However, this is in no way sufficient. In order to model the switching losses of Q1, you must accurately model both the charging current and the discharging current of the driver as it charges and discharges the Gate-to-Source capacitance of the power switch Q1 during the turn-ON and turn-OFF transitions.

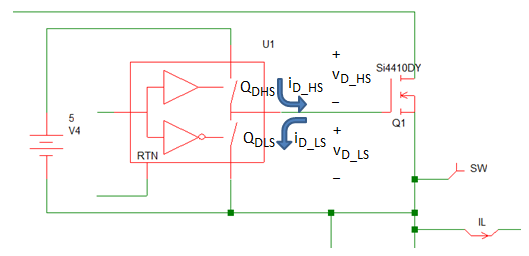

To make the necessary changes, follow these steps:

- To set up the output stage of the MOSFET driver, add MOSFETs

QDHS and QDLS in a totem-pole configuration

as shown below.

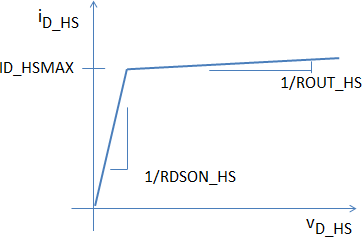

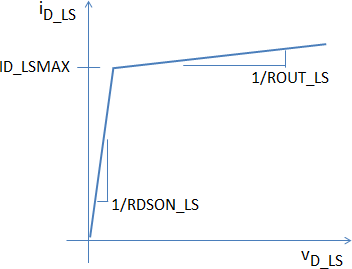

- To model the ideal switching behavior of the high-side driver MOSFET

QDHS and the low-side driver MOSFET

QDLS, characterize the output drive currents

iD_HS and iD_LS of the high-side driver

QDHS

and the low-side driver QDLS, as shown in the illustrations

below.

Now you can complete the detailed requirements of the driver model by saying that the driver must model the characteristics of QDHS and QDLS as shown above. In addition, you need to pass the the parameters RDSON_HS, ID_HSMAX, ROUT_HS, RDSON_LS, ID_LSMAX and ROUT_LS to the driver model.

Step 3: Create Driver Model

In the previous two figures, it was assumed that the characteristics of QDHS and QDLS are likely different in both their respective values of RDSON as well as in their maximum current capability ID_HSMAX and ID_LSMAX. This also assumes that the gate drive for both QDHS and QDLS is constant and independent of the loading of the driver output.

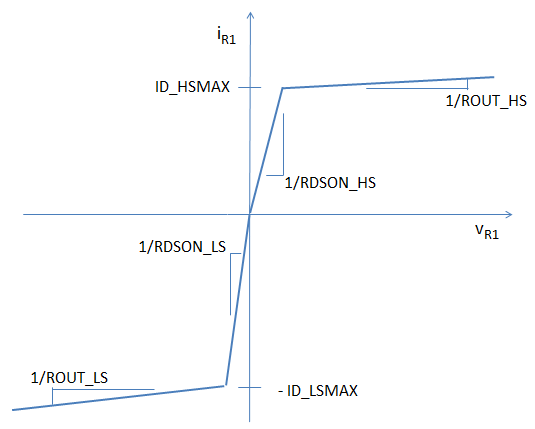

Looking at the iD_HS versus vD_HS characteristics of QDHS, the driver high-side MOSFET, it is clear that this behavior can be modeled in SIMPLIS by a PWL resistor. The same is true for QDLS, the driver low side MOSFET. In fact both QDHS and QDLS can be modeled by a single PWL resistor as shown below.

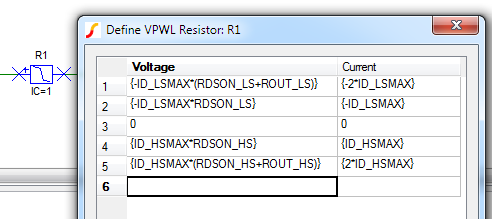

The definition of this PWL resistor is illustrated in this next figure, where the behavior of QDHS is shown in the first quadrant of the piecewise linear current iR1 versus voltage vR1 plot and the behavior of QDLS is shown in the third quadrant.

Based on the characteristics above, the PWL resistor R1 can be parameterized as shown here.

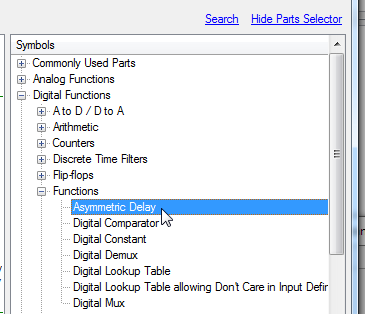

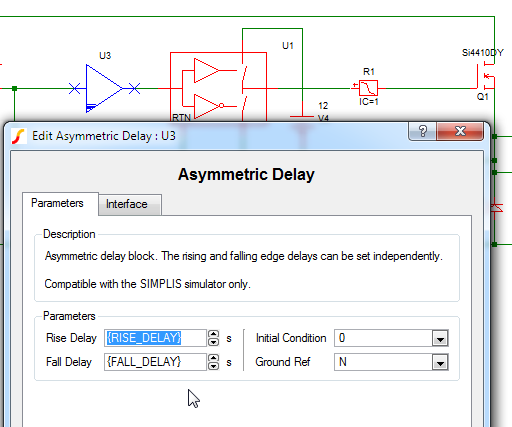

The final model requirement that needs to be addressed is the asymmetric delay of the input signal to the driver. Here the rise delay and the fall delay need to be parameterized independently.

After verifying that this flat driver test bench demonstrates the capability of meeting the original model requirements, it is time to create a driver subcircuit with an appropriate symbol and then parameterize it as indicated above. You can then refine the model as necessary, but should invest the majority of your testing efforts on the model in its final subcircuit form.

The schematic apps_a_flat_development_schematic.sxsch is the final flat schematic before converting the driver to a subcircuit. At this point, you are ready to create a subcircuit for the MOSFET Driver where its parameters are defined in the F11 window of the subcircuit.

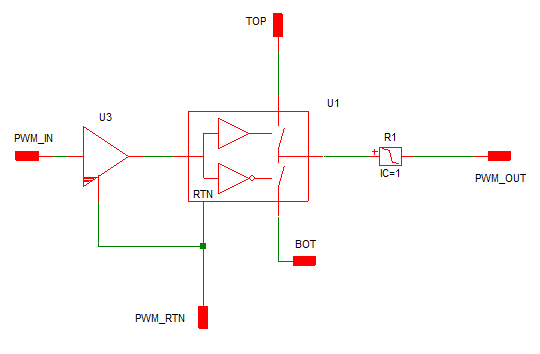

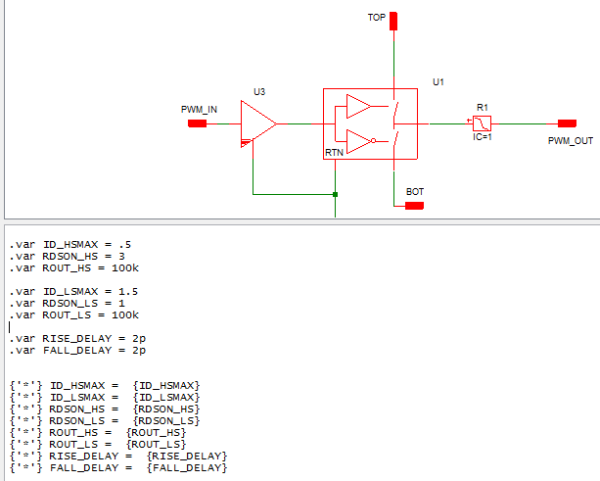

The following subcircuit schematic apps_a_driver_subcircuit_params_in_F11_window.sxcmp shows the driver model with both the asymmetric delay block and the PWL resistor parameterized as illustrated above.

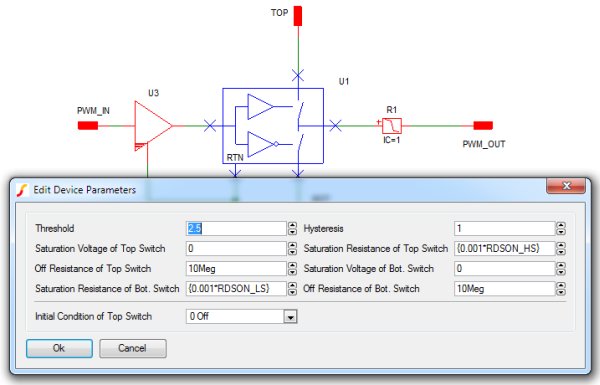

One aspect not yet addressed is the saturation resistance of the top and bottom switch in the driver block U1. When the top switch of U1 is ON, the possibility exists that the resistance of that top switch could be of a comparable resistance to the RDSON_HS parameter of the PWL resistor R1. In order to not have to worry about this possibility, you can parameterize the Saturation Resistance of the Top Switch to be a small fraction of RDSON_HS as shown here.

The same can be done for the Saturation Resistance of the Bot. Switch of U1. It can be made to be a small fraction of RDSON_LS.

Early in the subcircuit model development process, it makes sense to set the parameter values by using .var statements in the F11 window of the subcircuit itself as is the case with apps_a_driver_subcircuit_params_in_F11_window.sxcmp

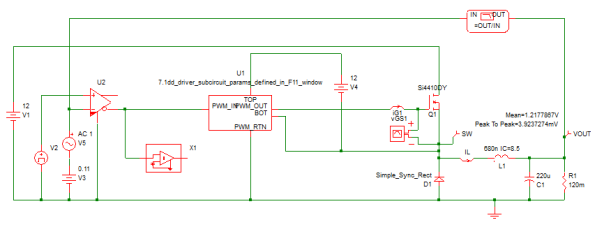

This allows you to focus your initial efforts on the correct parameterization of each of the elements in the subcircuit model. It also facilitates the initial verification of the subcircuit performance in the development test bench. As can be seen in this test bench apps_a_3_sync_buck_w_driver_no_GUI.sxsch , you are using the default, automatically created symbol and there is no GUI to facilitate changing the subcircuit parameter values from the symbol on the top level schematic.

However, once the functionality of the model is confirmed, it quickly becomes worthwhile to invest in adding the needed properties to the symbol allowing parameter values to be passed through the subcircuit symbol as described in Module 5. It will also be worth the modest time investment to enhance the look of the symbol if this modeling block can be reused in future projects.

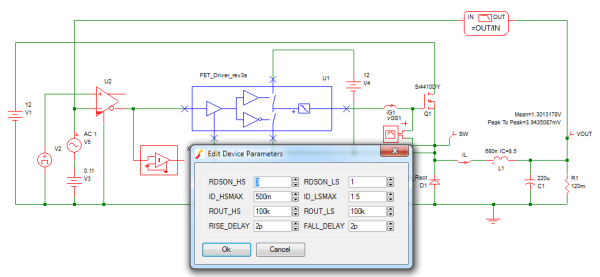

Here the schematic apps_a_4_sync_buck_w_parameterized_driver_w_GUI.sxsch presents a more informative symbol and a GUI dialog box for this driver subcircuit that was created using the steps described in Module 5 on Parameterization.

Step 4: Create Driver Test Benches

Since the ultimate objective is the evaluation of MOSFET switching losses with the driver model, at least two test bench circuits are needed. The first is to test the driver model itself. The second is to test the driver model while driving an N-channel MOSFET.

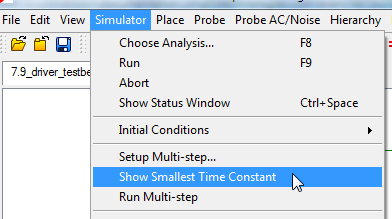

For each test bench, you will record several metrics to characterize the simulation performance of the driver test bench combination. After each simulation, you will record the minimum time constant of the test bench circuit as well as the number of new topologies needed to reach steady state. As soon as the simulation is complete, you will select the Show Smallest Time Constant menu item from the Simulator menu.

You also look in the SIMPLIS status window and record the number of new topologies required to reach steady state. The results of these queries are pasted underneath each test bench schematic.

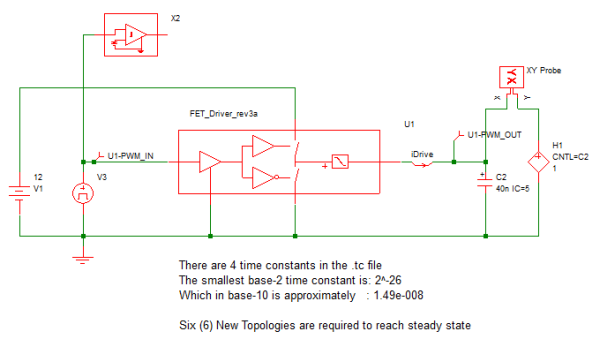

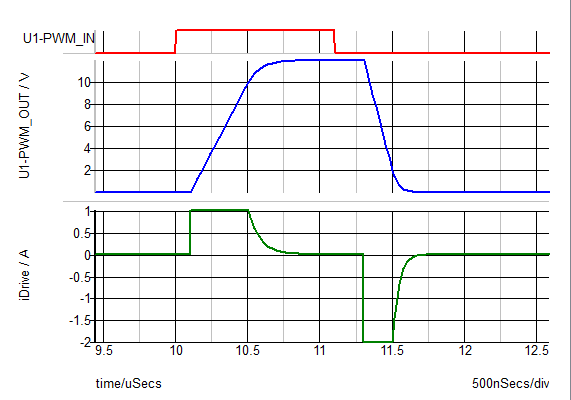

In the first test bench apps_a_5_driver_test bench_cap_load.sxsch, you test the driver modeling block with a pure capacitive load.

This is a good way to make sure that the driver block is behaving as expected. As you can see, when the capacitor voltage is initially rising, it is being charged with essentially a constant current source. Once the voltage across the PWL resistor R1 inside the driver model reaches a value of ID_HSMAX * RDSON_HS or less, then the charging current iDrive begins an exponential RC decay. The discharge current behaves in an analogous fashion.

It is easy to verify the key drive model break points from a graph of iDrive versus vPWMout.

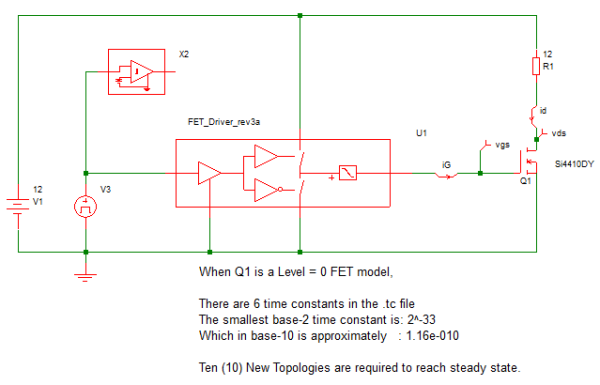

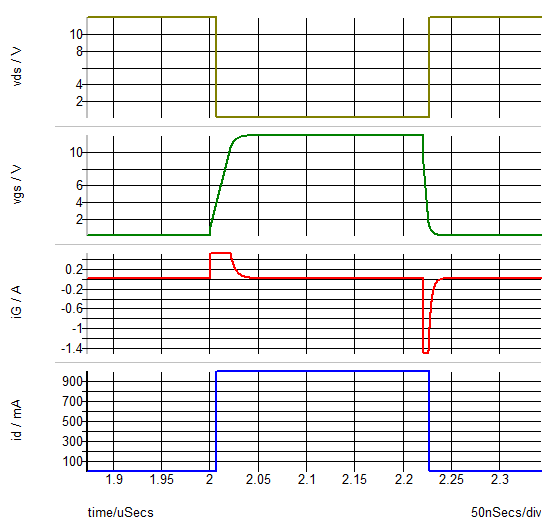

The next two test benches look at the performance of the combination of the driver model and an NMOS device driving a resistive load. In the first case, apps_a_6_driver_test bench_Lev0_mos_load.sxsch, the power switch is modeled with a Level 0 MOSFET model, which models the gate capacitance and exhibits instantaneous switching when the device turns ON or OFF.

The resulting steady-state waveforms generated by apps_a_6_driver_test bench_Lev0_mos_load.sxsch show the instantaneous switching as well as the same charging and discharging behavior of the gate capacitance as observed in the test bench with the pure capacitive load. The only slight difference is that at the initiation of turn ON and turn OFF, you can see the effect of the 1.55 Ohm gate resistance of the Si4410DY MOSFET.

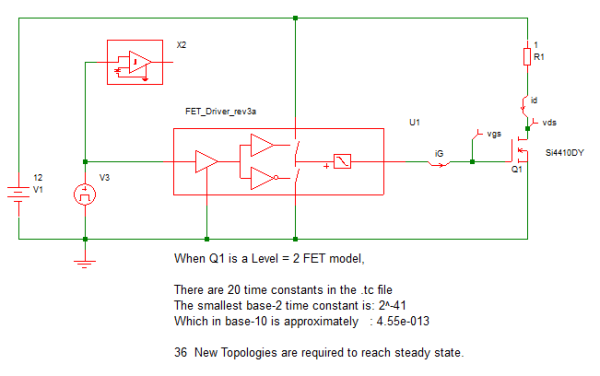

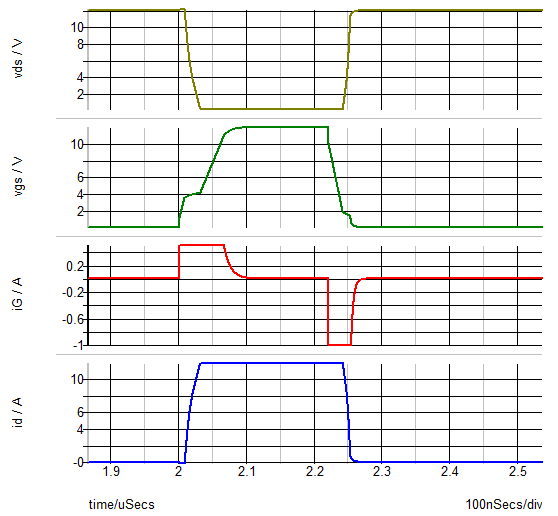

The next test bench apps_a_7_driver_test bench_Lev2_mos_load.sxsch changes the MOSFET model level from 0 to 2. It is still using a resistive load.

The resulting waveforms show the expected Miller effect during turn ON and turn OFF. Note that the number of new topologies increases significantly when you go from a Level 0 MOSFET model to Level 2. You also can see that the minimum time constant is three orders of magnitude smaller with the Level 2 model. Bear in mind that these results are for a greatly simplified case of a model of the synchronous MOSFET, modeled here as D1.

These results verify that this driver model is capturing the behavior intended and that the model construction is sound. You also get a good quantitative sense of the complexity of the driver model which will allow you to better predict what kind of simulation performance you can expect when you add this driver model into larger and more complex systems.

In the next step, you will test to see if you can use this driver model to obtain meaningful estimates of switching losses of the high side MOSFET in a synchronous buck dc-to-dc converter.

Discussion

It cannot be emphasized strongly enough that for high efficiency conversion systems, getting accurate estimates of overall efficiency requires that the system be in steady state. Output transients must be fully settled out in order to obtain accurate results. Without a successful POP analysis, you must exercise extreme patience in running long transients to allow the system to reach steady state.

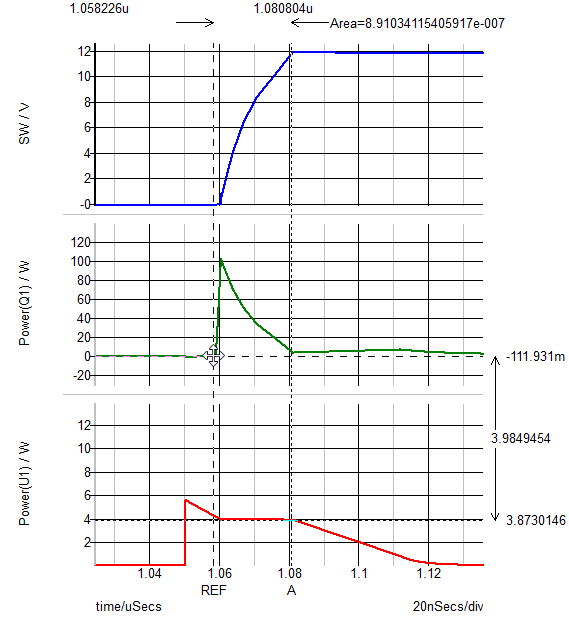

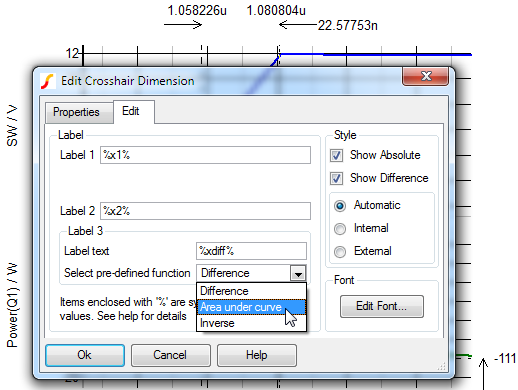

The above discussion focuses on average losses over a complete steady-state switching cycle. When optimizing the combined design of a driver and a MOSFET, you often need to look at the component portions of the switch losses, turn ON, turn OFF and conduction losses. There are a number of ways to do this. One easy way is shown here.

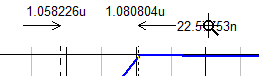

Notice that you have calculated the area under the instantaneous power dissipation curve for Q1 during the turn ON transition. To accomplish this, you set the cursors at the beginning and the end of the turn ON transition and then double click on the time difference display. This action opens a dialog window that allows you to request the display of the area under the selected curve between the REF and A cursors.

The result is that you have now calculated the energy dissipated in the MOSFET during each turn ON transition. In this case, 0.89 uJ, which at 500 kHz results in a loss of 0.445 W.

Using the same approach to measure the turn OFF losses, you obtain 0.53uJ of turn OFF energy, which results in a loss of 0.265 W. The nice thing about this approach is that you can scale the loss results by the switching frequency, which can be convenient when trying to optimize the overall design.

As is clear from the waveforms above, you could use the same approach to examine the losses in the driver circuit.

This modeling approach provides a powerful method for optimizing the design of a driver - power switch combination. The parameterization of the driver allows you to independently control the turn ON and turn OFF driver characteristics. The analysis approach allows you to optimize the driver characteristics, the power MOSFET selection according to the application requirements. This modeling approach for the driver is applicable to many different topologies and control laws.

Conclusions and Key Points to Remember

- Create a development test bench for your model at the very beginning.

- Develop your model incrementally. Using the development test bench continuously ,test the model from the very beginning. Smaller quicker steps win the race.

- It is okay to start your model development with a flat schematic, but transition to a hierarchical schematic as soon as feasible.

- The half life of a large flat schematic is inversely proportional to ( the modeler's age - 30 )^2.

- Create test benches for the final model and each critical component in it.

- Measure the minimum time constant and number of new topologies associated with the model.

- Measure the minimum time constant and number of new topologies associated with the combination of the model and any other critical sources or loads. In this case, it is essential to characterize the driver model in combination with the level 2 MOSFET model.