Up Counter

The Up Counter models a generic up counter with between 2 and 32 output bits.

- On each clock edge, the D0 ... Dn outputs can increase one count or hold the last count, depending on the EN pin.

- The clock-edge trigger can be set with the Trigger Condition parameter to be either rising edge (0_TO_1) or falling edge (1_TO_0).

- The counter may also be reset to a value with the RST pin. When the RST pin goes active, the counter changes to the value specified by the Reset To parameter.

- The Reset Type parameter controls whether the reset event is asynchronous or synchronous to the CLK edge.

For a counter which counts down, see Down Counter. For a counter that counts up or down, see Up/Down Counter.

In this topic:

| Model Name: | Up Counter | |||

| Simulator: |  |

This device is compatible with the SIMPLIS simulator. | ||

| Parts Selector Menu Location: | ||||

| Symbol Library: | None - the symbol is automatically generated when placed or edited. | |||

| Model Library: | None - the model is automatically generated when the simulation is run. | |||

| Subcircuit Names: |

|

|||

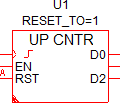

| Symbol: |

|

|||

| Multiple Selections: | Only one device at a time can be edited. | |||

Editing the Up Counter

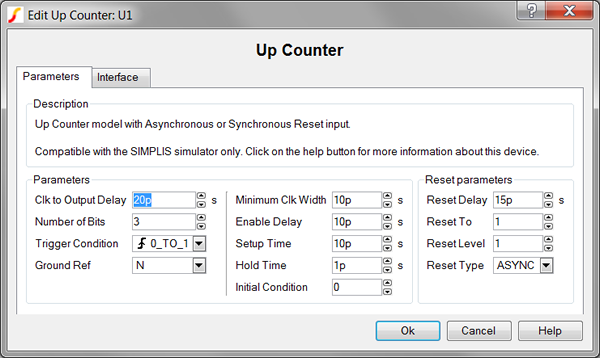

To configure the Up Counter, follow these steps:

- Double click the symbol on the schematic to open the editing dialog to the Parameters tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description | ||||||

| Clock to Output Delay | Delay from the triggering clock event until the Counter outputs change | ||||||

| Number of Bits | Number of output bits for the Counter | ||||||

| Trigger Condition | Determines the

triggering condition of the Counter clock pin:

|

||||||

| Ground Ref | Determines whether or not a device has a ground reference pin. Any digital component that has an input or output pin connected to an analog circuit node must have its Ground Ref pin connected to an analog node. This is usually the ground on the schematic. | ||||||

| Minimum Clk Width | Minimum valid clock width. Clock widths less than this parameter will not trigger the Counter. | ||||||

| Enable Delay | Delay from when the enable pin goes active until the output is enabled | ||||||

| Setup Time | Minimum time before the triggering clock event that the input signals must remain steady so that a valid change in each input state is recognized. | ||||||

| Hold Time | Minimum time after the triggering clock event that the input signals must remain steady so that a valid change in each input state is recognized. | ||||||

| Initial Condition | Initial condition of the Counter output at time=0 | ||||||

| Reset Delay | Delay from when the RST pin goes active until the counter output is reset | ||||||

| Reset To | Determines the value of the counter output when the RST pin goes active. To reset to 0, assign a assign value of -1 or 0. | ||||||

| Reset Level | Determines the Reset

level of counter RST input pin:

|

||||||

| Reset Type | Determines whether or

not reset events are synchronized with a clock event

|

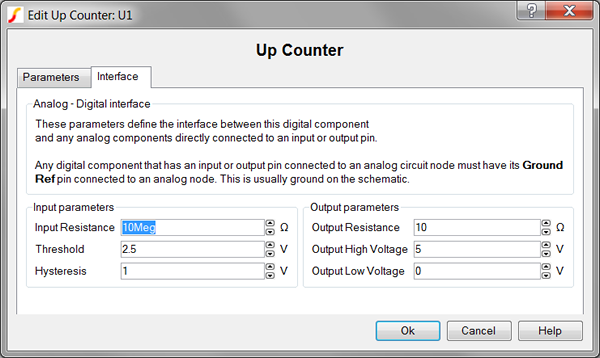

To define the parameters for the interface between this digital component and each analog component connected directly to an input or output pin, follow these steps:

- From the Edit Up Counter dialog box, click on the Interface tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description | |||||||

| Input Resistance | Input resistance of each Counter input pin | |||||||

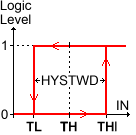

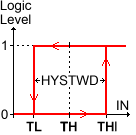

| Hysteresis, Threshold |  |

Hysteresis and

Threshold of the inputs. The hysteretic-window width, HYSTWD

is centered around Threshold (TH) voltage. To

determine the actual threshold ( TL , THI ),

substitute Threshold (TH) and Hysteresis

(HYSTWD) in each of the following formulas:

|

||||||

| Output Resistance | Output resistance of each Counter output pin | |||||||

| Output High Voltage | Output high voltage for each Counter output pin | |||||||

| Output Low Voltage | Output high voltage for each Counter output pin | |||||||

Truth Table

The following truth table assumes a Trigger Condition=0_TO_1 which represents a rising edge clocked counter.

| Inputs | Outputs | Action | ||

| EN | RST | CLK | D0..Dn | |

| 1 | 0 |

|

Count + 1 | Count up |

| 0 | 0 |

|

Last count | Retain last count |

| 0 | 1 | 0 or 1 | Reset To parameter value | Reset the counter to the Reset To parameter value |

Examples

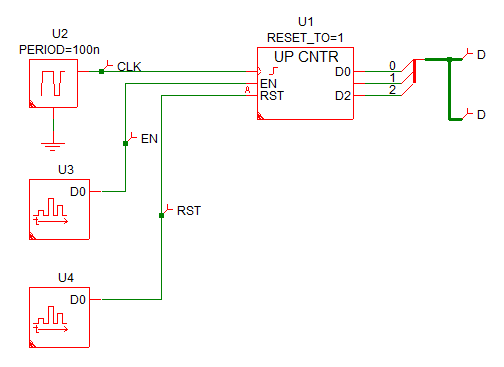

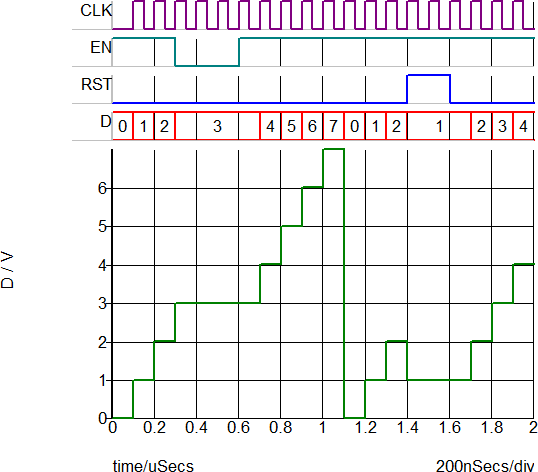

The test circuit used to generate the waveform examples in the next section can be downloaded here: simplis_028_upcounter_example.sxsch.

Waveforms

Subcircuit Parameters

Because the Up Counter model is generated by a template script when the simulation is executed, a hand-coded model cannot be inserted into a netlist. The template script for this device is simplis_make_counter_model.sxscr, which licensed users can download as part of a zip archive of all built-in scripts.

To download the zip archive, follow these steps:

- Click http://www.simetrix.co.uk/simetrix80/scripts.zip to download the script archive.

- Enter the user name and password you received with your license file.

The following parameter table defines the parameters used in this model.

| Parameter Name | Label | Data Type | Range | Units | Parameter Description | |||||||

| CLK_TO_OUT_DELAY | Clock to Output Delay | Number | 1f to 1024 | s | Delay from the triggering clock event until the Counter outputs change | |||||||

| ENABLE_DELAY | Enable Delay | Number | any | s | Delay from when the enable pin goes active until the output is enabled | |||||||

| GNDREF | Ground Ref | String |

|

none | Determines whether or not a device has a ground reference pin. Any digital component that has an input or output pin connected to an analog circuit node must have its Ground Ref pin connected to an analog node. This is usually the ground on the schematic. | |||||||

| HOLD_TIME | Hold Time | Number | 1f to 1024 | s | Minimum time after the triggering clock event that the input signals must remain steady so that a valid change in each input state is recognized. | |||||||

| HYSTWD, TH |

Hysteresis, Threshold |

Number | min: 1f | V |  |

Hysteresis and Threshold of

the inputs. The hysteretic-window width, HYSTWD is centered around

Threshold (TH) voltage. To determine the actual threshold (

TL , THI ), substitute Threshold (TH) and

Hysteresis (HYSTWD) in each of the following formulas:

|

||||||

| IC | Initial Condition | Number |

|

none | Initial condition of the Counter output at time=0 | |||||||

| MIN_CLK | Minimum Clk Width | Number | 1f to 1024 | s | Minimum valid clock width. Clock widths less than this parameter will not trigger the Counter. | |||||||

| NUMBITS | Number of Bits | Integer | none | Number of output bits for the Counter | ||||||||

| RESET_DELAY | Reset Delay | Number | any | s | Delay from when the RST pin goes active until the counter output is reset | |||||||

| RESET_LEVEL | Reset Level | Integer | none | Determines the Reset level of

counter RST input pin:

|

||||||||

| RESET_TO | Reset To | Number | none | Determines the value of the counter output when the RST pin goes active. To reset to 0, assign a assign value of -1 or 0. | ||||||||

| RESET_TYPE | Reset Type | String |

|

none | Determines whether or not

reset events are synchronized with a clock event

|

|||||||

| RIN | Input Resistance | Number | min: 100 | Ω | Input resistance of each Counter input pin | |||||||

| ROUT | Output Resistance | Number | min: 1m | Ω | Output resistance of each Counter output pin | |||||||

| SETUP_TIME | Setup Time | Number | 1f to 1024 | s | Minimum time before the triggering clock event that the input signals must remain steady so that a valid change in each input state is recognized. | |||||||

| TRIG_COND | Trigger Condition | String |

|

none | Determines the triggering

condition of the Counter clock pin:

|

|||||||

| VOH | Output High Voltage | Number | any | V | Output high voltage for each Counter output pin | |||||||

| VOL | Output Low Voltage | Number | any | V | Output high voltage for each Counter output pin | |||||||